|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

第77回応用物理学会秋季学術講演会(9月13〜16日) |

|||||||||||

9月13〜16日、朱鷺メッセ(新潟県新潟市)で開かれた「第77回応用物理学会秋季学術講演会」。有機EL、有機TFT、酸化物TFT、プロセス技術のなかから注目講演をピックアップする。 対向スパッタ成膜したカソード素子は成膜時の基板温度上昇がないため発光電圧が上昇 対向スパッタリング法で成膜したメタルカソードを用いた有機EL素子を研究している東京工芸大学の研究グループは、Alカソード成膜時の基板温度がデバイス特性にどう影響するのかについての研究成果を報告した。 これまで研究グループは高エネルギー電子の基板入射を抑制するとともに、高エネルギースパッタリング粒子の基板への入射を抑制するために6mTorr以上のスパッタガス圧で成膜することにより、良好な発光特性を有する素子が作製できることを報告してきた。しかしながら、発光開始電圧は8〜10Vと、蒸着法で作製した従来素子に比べ4〜5V高い。その原因を調べるため、Alカソード成膜時の基板温度とデバイス特性の関係を調べた。 実験では、ガラス基板上に対向ターゲット式スパッタ法でITOアノードを膜厚80nmで成膜した後、8mTorrのAr+10%O2混合ガス雰囲気において60mA、480Vという条件で30秒間スパッタ成膜することにより厚さ約0.6nmのITOバッファ膜を成膜した。この後、NPBホール輸送層(40nm)/Alq3発光層(30nm)/BCP電子輸送層(30nm)/LiFバッファ層(0.6nm)を蒸着。続いて、対向ターゲット式低ダメージスパッタ源および抵抗加熱蒸着源を用いて厚さ約50nmのAlカソード膜を成膜して素子を作製した。熱電対を基板位置に配置し、WAHL Instrumentsのサーモプレートを基板上に張る方法で成膜時の基板の温度上昇を測定した。この結果、蒸着中の基板温度は所望の厚さまで蒸着すると基板裏面でも約80℃に達するのに対し、スパッタ成膜時には基板の温度上昇がほとんど認められず、43℃のサーモプレートも変色しないことがわかった。 通常のスパッタ法と蒸着法で作製した素子、蒸着中の基板温度上昇を抑制して作製した素子、スパッタ法で作製した素子を真空中で低温熱処理した素子の電圧-電流特性、電圧-発光特性を評価したところ、蒸着法でも成膜時の基板温度上昇を43℃以下に抑制すると動作電圧が上昇してスパッタ法で作製した素子の特性に近づくこと、またスパッタ成膜した素子を真空中で加熱処理すると動作電圧は大幅に低下し通常の蒸着法で作製した素子の特性に近づくことがわかった。この結果は低ダメージスパッタ法と蒸着法で作製した素子の動作特性の違いがおもに成膜時の基板温度上昇で説明できることを示している。

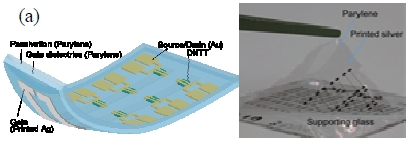

凸版反転印刷したAgをゲートを用いて基板レス構造有機トランジスタを実現 理化学研究所、科学技術振興機構(JST)、東京大学の研究グループは、凸版反転印刷法で形成したAg電極をゲートとして用いた基板レス構造有機トランジスタについて報告した。 実験では、まずガラス基板上にテフロン(AF1600)をスピンコート成膜して剥離層を形成。続いて、凸版反転印刷法でAgナノ粒子インク(RAGT-29)を印刷し、180℃×1時間焼成してゲート電極を形成した。膜厚は75nmである。次に、ゲート絶縁膜兼基板フィルムとしてパリレン(diX-SR)を気相重合成長により膜厚300nmで成膜した。半導体層にはジナフトチエノチオフェン(DNTT)を膜厚30nm、ソース・ドレイン電極にはAuを50nmを真空蒸着。最後に、膜厚300nmでパリレンを成膜して封止した(図1-a)。支持基板から剥離後、素子全体の膜厚は755nmである。

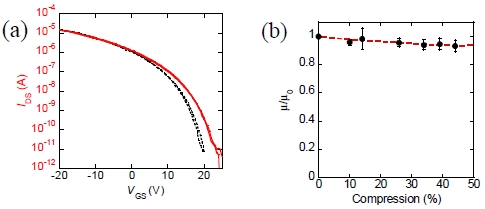

反転印刷時のインク塗布速度によってAg電極の膜厚を75〜500nmまで制御可能で、塗布速度1mm/sの際に最小膜厚75nmが得られた。また、この電極がテフロン剥離層から完全に剥離し、パリレン絶縁膜へ転写されることが確認できた(図1-b)。この電極をゲート電極として用いることにより、図2のように良好に動作するトランジスタが実現できた。支持ガラスから剥離した後のキャリアモビリティは0.48cm2/V・sで、蒸着Auゲート電極を用いた場合と同程度の性能が得られた。また、ソース・ドレイン電流の向きに垂直な方向への歪みを加えた場合、60%の歪みを加えてもモビリティの変化は4.3%に過ぎなかった。 a-ITZOは光照射ストレス耐性でa-IGZOより有利? すでにLCD用アクティブマトリクス素子として実用化されている非晶質InGaZnO(a-IGZO)-TFT。しかしながら、代表的なアモルファス酸化物TFTであるa-IGZO-TFTは負バイアスストレス下での光照射(NBIS)によるしきい値電圧シフトが知られており、いまだ完全に解決できているとは言い難い。今回、日本大学の研究グループはa-IGZO-TFTとa-ITZO-TFTに劣化条件を与えて前後の測定結果を比較した成果を報告した。

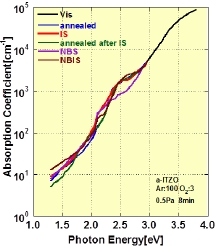

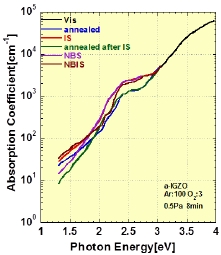

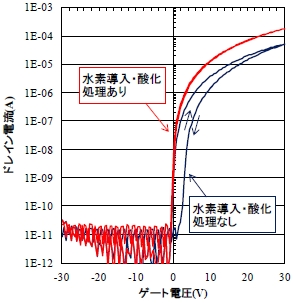

実験では、2×2cmのノンアルカリガラス基板上にボトムゲート型TFTを作製した。DCマグネトロンスパッタ法によってa-IGZO膜とa-ITZO膜を室温下で300nm成膜した。このサンプルに各条件を与えて反射CPM評価を行った。具体的には、白色光1.12×10-1W/cmをゲート電圧-10V印加条件で1時間照射する光ストレス(IS)を与えた。なお、熱処理は空気中において350℃×1時間行った。 図3、4にストレス印加とアニール処理後の反射CPMスペクトルを示す。成膜後のサンプルを350℃×1時間熱処理した場合の吸収係数を基準とし、ゲート負バイアス下での光照射を与えることにより、a-IGZOは1.5eVおよび2.4eVの光吸収係数が顕著に上昇した。これに対し、a-ITZOはa-IZGOに比べストレスを印加した際、1.5eVおよび2.4eV付近の光吸収係数の顕著な上昇が確認できなかった。とくに、1.5eV付近の準位は信頼性に大きく影響を与えることが知られている。このことから、a-ITZOはa-IZGOに比べ負バイアスストレス下光照射における劣化が少なく、ストレス状態においても高い信頼性を有すると考えられる。 NHK放送技術研究所は、塗布型IGZO-TFTの焼成温度を低温化するため水素導入と酸化処理の連続プロセスを適用したデバイスについて報告した。

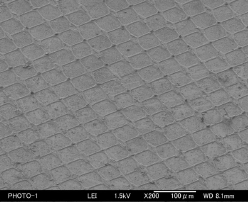

半導体前駆体溶液は硝酸インジウム、硝酸ガリウム、硝酸亜鉛を所定の割合で調整し、水溶媒に溶解・撹拌することによって作製した。ゲート絶縁膜として用いる熱酸化SiO2膜付きSiウェハー上にIGZO前駆体をスピンコートし、マックス250℃で焼成してIGZO膜を成膜した。フォトリソでIGZO膜をアイランド化した後、水素プラズマによる水素導入処理と250℃アニールによる酸化処理を行った。最後に、メタルマスクを用いてMoソース/ドレイン電極を形成してTFTを作製した。 図5に水素導入・酸化処理ありの場合とレスの場合の伝達特性を示す。250℃といった比較的低温下でのプロセス温度においてもこれらの処理が有効で、キャリアモビリティが1.1cm2/V・sから3.1cm2/V・sに向上し、ヒステリシスも抑制されることが確認できた。さらに、Positive Bias StressおよびNegative Bias Stress評価を行って特性安定性を評価した結果、バイアスストレス下でのしきい値電圧シフトの抑制にも効果があることがわかった。これらは、水素導入による不純物低減、酸化処理による酸素欠損の低減などがバイアスストレス下における安定性改善に起因するためと考えられる。 スクリーンメッシュを用いた簡易プロセスでCuメッシュを作製 産業技術総合研究所(産総研)は、ITO透明電極の代替として期待されている金属グリッド電極、なかでもローコストなCuグリッド電極をコンベンショナルなフォトリソグラィを用いずに、スクリーンメッシュを鋳型としたマスクパターン形成法を用いて作製したことを報告した。 まず、ポリエチレンナフタート(PEN)フィルム上にCu薄膜(1μm厚)をスパッタリング成膜。その上に325〜500メッシュのスクリーンマスクをのせ、ポリビニルアルコール(PVA) を主成分とする高分子水溶液(0.5wt%)をスクリーンメッシュ全体に広がる程度で滴下した。この結果、スクリーンメッシュとCu薄膜表面の間を毛細管現象によりPVAが広がり、乾燥過程でほぼスクリーンメッシュを転写したようなPVAパターンが形成される。これをマスクにして、塩化鉄(FeCl3)メタノール溶液によってCu膜をエッチングした。この結果、PVAマスクパターン通りのCuグリッドパターンがPENフィルム上に残る。

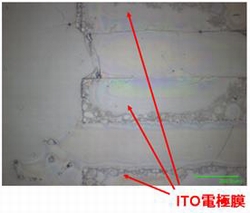

作製したCuグリッド電極は線幅2.5μmで、透過率は90%以上、面抵抗は十数Ω/□を示した。SEM観察、触針段差計によりPVAはCuグリッド電極を被覆しており、パターン下のエッチング、いわゆるアンダーカットがほとんどみられなかった。PVAが被覆されることで塩酸ガスへの曝露や加熱処理による酸化腐食が抑制され、PVAを除去した場合に比べ耐久性が高いことがわかった。また、2枚の銅グリッド電極をPVAが重なるように挟み込むことにより電極に加わる圧力変化による静電容量の変化が確認でき、圧力センサーとして機能することが確認できた。 ミストデポジション法の特徴を活かしてレジストフリーでITO膜をパターニング ニコンは真空成膜法、ウェットコート法に次ぐ第3のデポジション法として知られるミストデポジション法を用いてフォトレジストフリーでITO透明導電膜をパターニングしたことを報告した。ミストが即座に蒸発せずに液滴として振る舞うことを利用したニュープロセスで、大面積基板やRoll to Rollプロセスにも容易に対応可能としている。 実験では、石英基板をサブストレートに使用。まず基板上にフッ素化撥水膜をスピンコート成膜する。この後、シャドーマスクを基板表面に載置し、UV処理によって表面改質する。この結果、UV光が照射された部分は撥水性から親水性に変化する一方、マスキングによって照射されなかった部分は本来の撥水性を維持する。続いて、ITOナノ粒子分散液をミストデポジション法によってスプレー噴霧する。この際、2.4MHzの超音波振動子によって分散液を霧化する。分散溶媒が水の場合、ミスト径は5μm程度で、Arキャリアガスによって基板上にトランスポートする。

この結果、写真2のようにITOは親水部分にのみ選択的に付着する一方、撥水部分にはミストが液滴として振る舞うため付着せず、レジストフリーの自己整合プロセスが実現する。 参考文献 |

|||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |

|