|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

映像情報メディア学会技術報告-情報ディスプレイ-(7月30日) |

|||||||||||||||||||||||||||||||

7月30日、東京・機械振興会館で「映像情報メディア学会技術報告-情報ディスプレイ-」が開かれた。5月の「SID 2018」で紹介されたオーラル講演の一部を再ピックアップしたもので、フレキシブルディスプレイ向けテクノロジーの発表が多かったように感じた。ここでは、JOLEDとジャパンディスプレイの酸化物TFTについての発表2件をクローズアップする。 PIベース酸化物TFTの信頼性改善には体積抵抗の高いPIを用いる必要が JOLEDの田中正信氏は「高信頼性TFTを達成するためのポリイミド基板についての報告」と題して講演、透明ポリイミド(PI)をサブストレートに用いたフレキシブル酸化物TFTの信頼性について報告した。

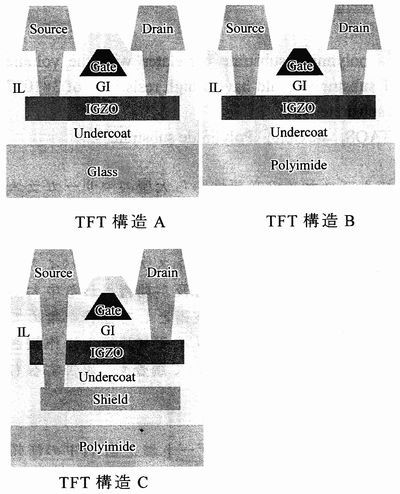

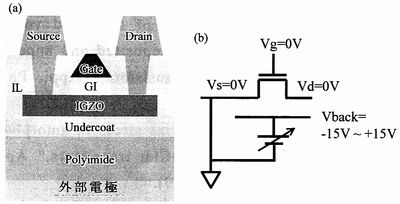

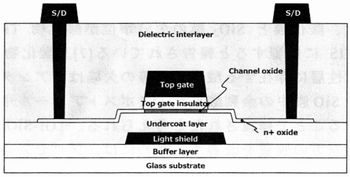

作製プロセスはいずれも共通で、①SiO/SiN膜をCVD成膜してアンダーコート層を形成する、②IGZO膜をスパッタリング成膜しフォトリソでパターニングする、③SiO膜を成膜してゲート絶縁膜を形成する、④Al系メタルをスパッタ成膜しフォトリソでパターニングしてゲート配線を形成する、⑤AlO膜をスパッタ成膜し、IGZO領域にソース/ドレイン領域を形成する、⑥有機膜を成膜して層間絶縁膜を形成する、⑦メタル膜を成膜・パターニングしてソース/ドレイン電極を形成する、といった流れ。デバイスB、Cはガラス基板上にポリイミド膜(焼成後膜厚8μm)を塗布し焼成した後、上記のプロセスでIGZO-TFTを作製。最後に、ガラス基板裏面からエキシマレーザーを照射してポリイミド層の一部を昇華させてガラス基板からリリースした。

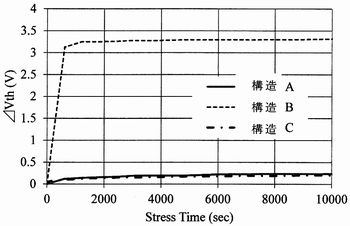

図2にBTS(Bias Temperature Stress)試験結果を示す。試験は温度50℃、N2雰囲気において行った。電圧印加10000秒後、デバイスAのΔvthは0.23V、デバイスCは0.21Vと良好な値が得られた。これに対し、デバイスBはΔvthが3.3Vと大きく変動した。これは、やはりポリイミドの存在に起因するためと考えられる。しかしながら、同じポリイミド基板製デバイスであるデバイスCは高い信頼性が得られている。

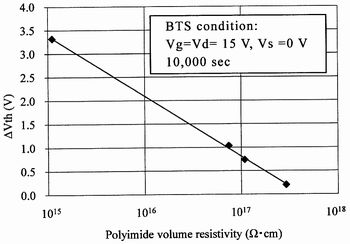

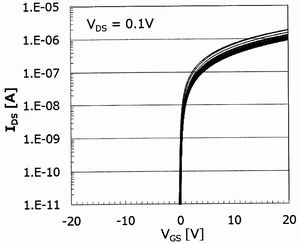

これらの結果、ポリイミド基板製TFTの信頼性劣化はポリイミド中の電荷移動によるものと考えられる。電極間に印加された電圧がポリイミド中に電界を形成して電荷が生成され残留・蓄積されて固定電荷となり、TFTのバックゲートのように作用して特性を変動させると推測される。ポリイミドが高抵抗なほど、同じ電界が印加されていても電荷が膜中移動できないため、電荷の影響が特性を劣化させるまでに時間を要して特性劣化が小さくなると考えられる。 PBTSはゲート絶縁膜成膜温度、NBTISはポストアニール温度に相関が 一方、ジャパンディスプレイの山口陽平氏はシート状TFT-LCD向けのトップゲート型酸化物TFTについて発表した。

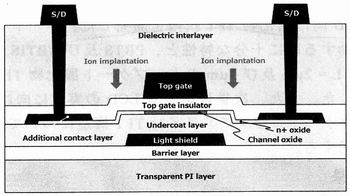

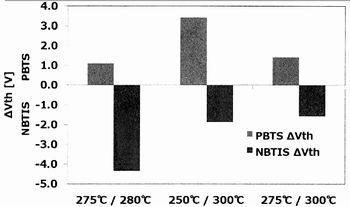

さらに、ゲート絶縁膜成膜温度とポストアニール温度がPBTSおよびNBTISにどのような影響を与えるかを調べた。その結果が図6で、総じてPBTSはゲート絶縁膜成膜温度が高いとΔVthが少なくなる一方、NBTISはポストアニール温度が高いとΔVthが小さくなるという傾向がみられた。 研究グループではIGZO-TFTをセレクタ回路内蔵型シートTFT-LCDにも適用させるため、セルフアライン構造のトップゲート型酸化物TFTも試作。構造は図7の通りで、イオン注入プロセスをレス化しゲート絶縁膜とゲート電極を一括パターニング。さらに、追加コンタクト層もレス化した。この結果、モビリティは21.16cm2/Vsにまで向上。イニシャルVth(0.82V)、オフ電流、PBTS(ΔVth=0.39V)とも良好な値が得られたが、NBTISでのΔVthは-5.28Vと大きく、今後、改善が必要なことがわかった。

1)田中正信ほか:高信頼性TFTを達成するためのポリイミド基板についての報告、映像情報メディア学会技術報告-情報ディスプレイ-資料、pp9-12(2018.7) 2)山口陽平ほか:フレキシブル基板へ向けたトップゲート酸化物TFTの開発、映像情報メディア学会技術報告-情報ディスプレイ-資料、pp13-16(2018.7) |

|||||||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |

フィルムマスクでガラスマスク並みの寸法安定性が得られます。 |