STELLA NEWS SITE is managed by Stella Corporation Inc. |

Technical Report of The Institute of Image Information and Television Engineers-Information Display- (July 30) |

|||||||||||||||||||||||||||||||

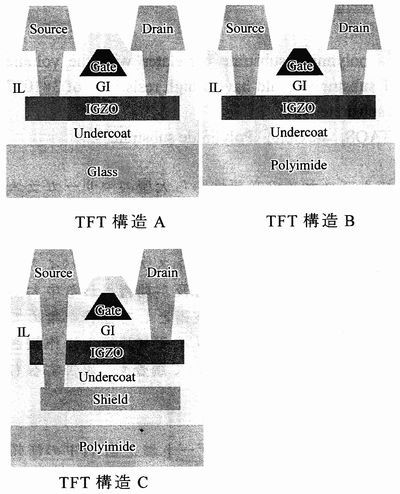

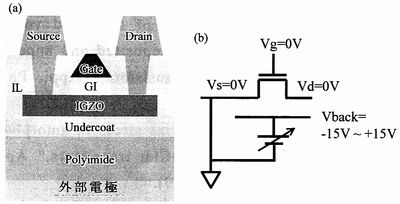

Technical Report of The Institute of Image Information and Television Engineers-Information Display- was held in Tokyo at July 30, 2018. In this here, two technical reports (JOLED and Japan Display) about flexible oxide-TFTs are picked up. Reliability of PI-based oxide-TFTs is enhanced by use of PI with high volume resistivity Mr.Tanaka (JOLED) reported reliability of flexible oxide-TFTs using transparent polyimide (PI) film in this presentation.

Manufacturing process is basically common;ć@Undercoat layer is formed by PE-CVD deposition of SiO/SiN films, ćAIGZO channel is formed by the sputtering deposition and photolithography, ćBGate insulator layer is formed by PE-CVD deposition of SiO film, ćCGate electrode is formed by the sputtering deposition of Al film and photolithography, ćDSource/drain region is formed in IGZO area by the sputtering deposition of AlO film, ćEInterlayer insulator film is deposited by coating of organic film, ćFSource/drain electrodes are formed by the sputtering deposition of metal film and photolithography.

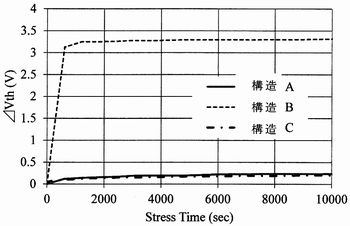

Table 1 shows device characteristics. Vth of these devices are almost same. However, carrier mobility and S factor of device C are relatively low and large respectively.

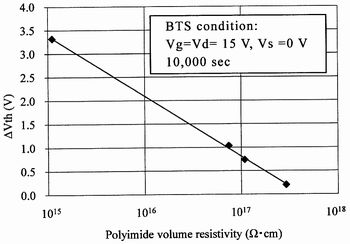

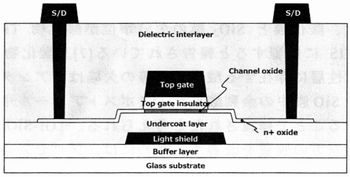

And, āóVth of device was different to correspond with kind of PI material. Figure 4 shows relationship of the volume resistivity of PI and āóVth. If the volume resistivity of PI is high, āóVth is low, as a result, device reliability is enhanced. As figure 4, if PI with 3ü~1017 āČźcm and over the volume resistivity is used, āóVth of TFT can be suppressed same as that of device A. PBTS and NBTIS are related on GI deposition temperature, post-annealing temperature respectively Mr.Yamaguchi reported top-gate oxide-TFTs for sheet type LCD. Figure 5 shows structure of pilot-produced device. First of all, a transparent polyimide (PI) film was coated on the 4.5 generation mother glass substrate. Finally, oxide-TFT with PI substrate was released from the original glass substrate by irradiation of excimer laser.

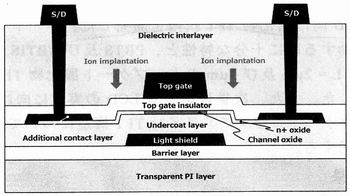

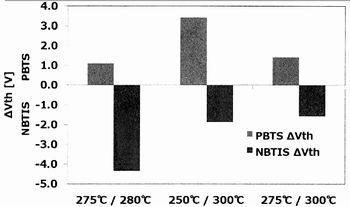

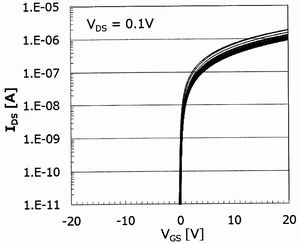

Figure 6 shows relationship of deposition and annealing temperature and reliability of IGZO-TFT. In general, if deposition temperature of gate insulator film is high, āóvth in PBTS was lowüGon the other hand, if post annealing temperature is high, āóVth in NBTIS was low. The research group has pilot-produced a self-align type top-gate IGZO-TFT, too. Figure 7 shows cross-section structure of this sample. Unlike with the above TFT, ion implantation process and additional contact layer were detected, and gate insulator film and gate electrode were patterned at the same time by common photolithography. As a result, carrier mobility was enhanced same as 21.16 cm2/Vs. Furthermore, initial Vth (0.82 V), off current, and āóVth in PBTS (0.39 V) were sufficient for the next generation sheet type LCD. By contrast, āóVth in NBTIS was insufficient same as -5.28 V.

1)Tanaka, et.al.üFRequirement of a Polyimide Substrate to Achieve High Thin-film-transistor Reliability, Technical Report of The Institute of Image Information and Television Engineers-Information Display-, pp9-12 (2018.7) 2)Yamaguti, et.al.üFDevelopment of Top-Gate Oxide TFTs for Plastic-Film LCDs, Technical Report of The Institute of Image Information and Television Engineers-Information Display-, pp13-16 (2018.7) |

|||||||||||||||||||||||||||||||

| REMARK STELLA NEWS SITE is a free news site of FPD and PCB by Stella Corporation Inc.(This company does not release these FPD and PCB related products.) |

|