FPD、PCB、次世代光源のニュースサイト STELLA通信 |

|

※STELLA通信は㈱ステラ・コーポレーションによって運営されています。 supported by Stella Corpration., Inc. |

Private View 第2回 |

|||||

近年、エレクトロニクスデバイス製造プロセスで存在感が高まっている自己整合技術。各種構造物を自動的にパターニングする技術で、工程数削減や超微細化などのメリットがある。今回はFPD製造プロセスで提案または採用されている自己整合プロセス技術のうち、グッドアイデアと首をかしげたくなるアイデアの双方を具体例を挙げてみてみる。なお、今回のコラムに関しても不快に思う開発担当者・読者もいると推測されるため、反論やコメント等があればこのメールアドレス宛て(info@stellacorp.co.jp)にご意見をおよせていただければ幸いである。

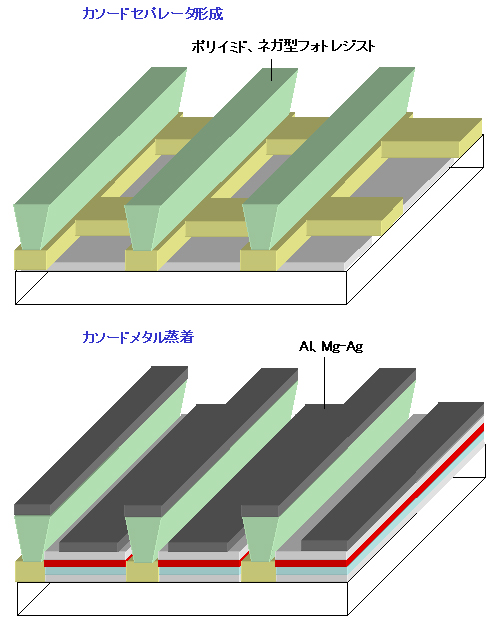

特性を低下させる(?)貼り合わせプロセス まずは有機ELディスプレイ関連から。この分野における代表的な自己整合技術といえばカソードセパレータだろう。パッシブマトリクスパネルの場合、カソードメタルを透明アノードと交差する格好でパターニングする必要があるが、下層から順に成膜する一般的なボトムアッププロセスではすでに有機EL層が形成されているため、カソードを一般的なフォトリソで形成することができない。そこで、考案されたのがカソードセパレータ。図1のように、感光性ポリイミドやネガ型フォトレジストを逆テーパー形状でストライプ上にパターニングする。この結果、その後、メタル膜をベタで蒸着しても上下にセルフパターニングされカソード電極として機能する仕組み。この工法はパッシブ有機ELDの量産当初から量産技術として確立されており、事実上のデファクトスタンダードとなっている。 これに対し、新工法として提案されているのがアノード基板とカソード基板を貼り合わせる貼り合わせ方式。前面基板にはITO/IZOアノード、ホール注入層、発光層を形成。一方、プラスチックフィルムなどにMg-Agなどのメタルカソードを成膜し、一般的なフォトエッチング法でパターニングしてカソード基板を作製する。そして、図2のように両面基板を160~200℃で加熱・圧着し貼り合わせる。いうまでもなく、このプロセスは有機層に対するダメージを考慮しなくていいため、カソードの成膜・パターニングが容易で、カソードセパレータが不要といったメリットがある。 このプロセスは一見理にかなっているようにみえるが、筋が悪い技術といわざるを得ない。貼り合わせ時の加熱温度や加圧力を最適化するとともに、さらにカソードメタル上へのバッファ層形成といった工夫を施しても、カソードから発光層へ円滑に電子がインジェクションできるかどうかがはなはだ疑わしいためだ。実際、このプロセスで作製したデバイスは学会発表などを聞く限り、コンベンショナルな積層デバイスに比べ特性が低下するという。いうまでもなく、有機ELDはまだ発展途上のデバイス。そうしたデバイスで特性を犠牲にすることなどあり得ない。厳しい言い方だが、上記の貼り合わせプロセスはデバイス特性を犠牲にする安易なメソッドといっても過言でないだろう。

自己整合隔壁形成法は特性やライフを損なう危険が

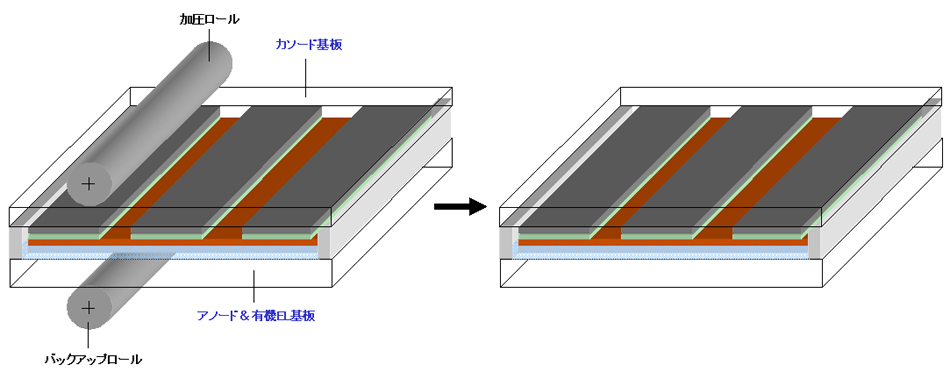

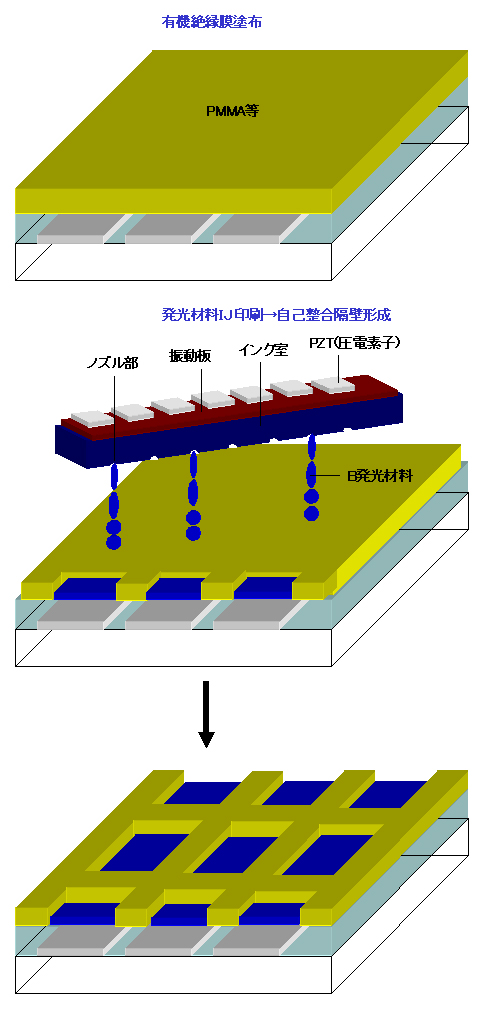

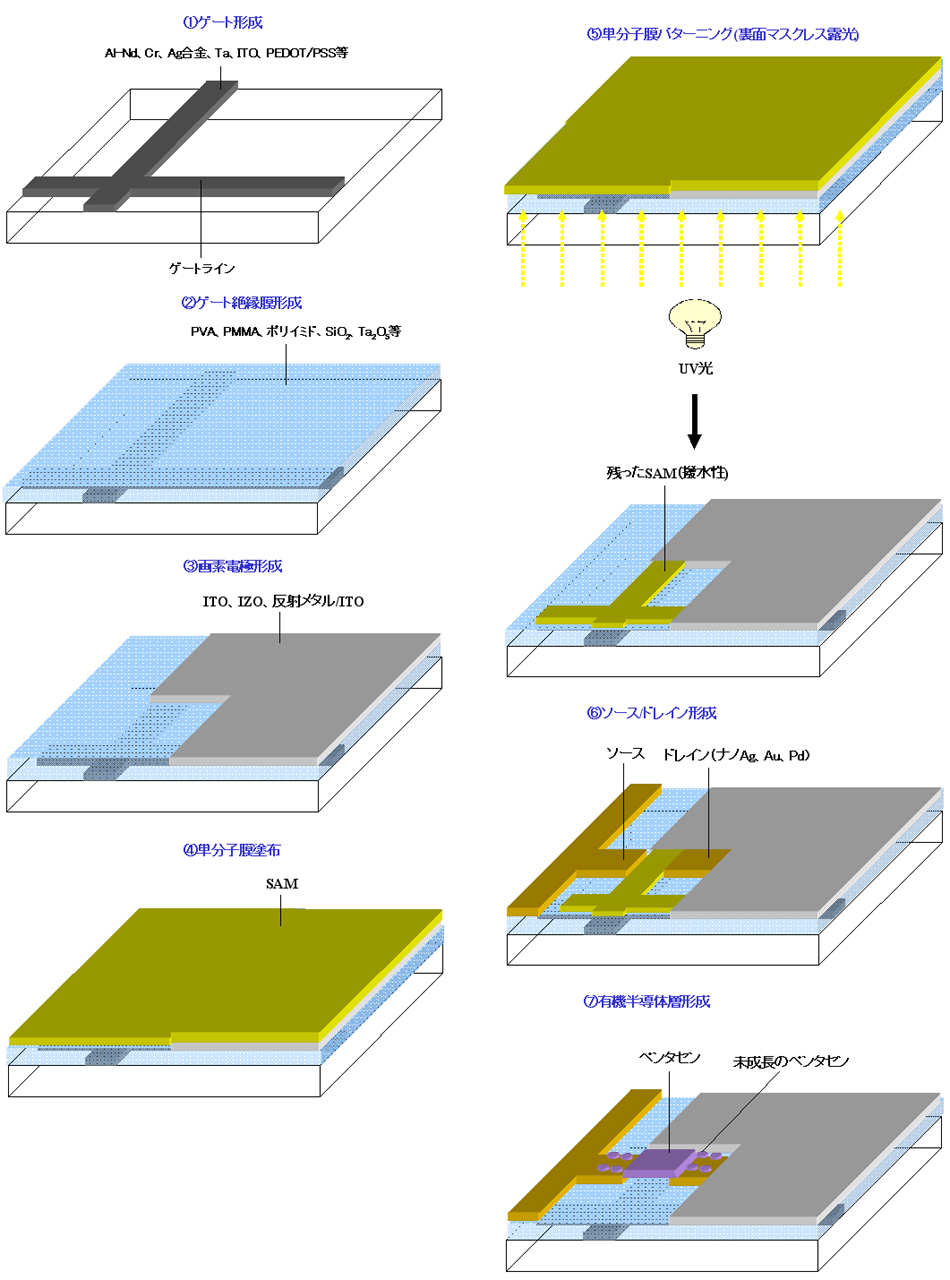

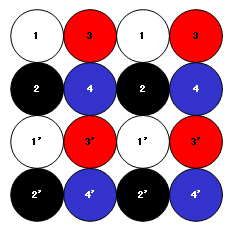

高分子有機ELDのバンク(隔壁)&発光層形成工程でもクエスチョンマークをつけたくなるプロポーザルがある。某大学から提案されている自己整合隔壁形成法で、発光ポリマーとバンクを一括形成するのが特徴。 図3のように、アノードもしくはホール注入層上にまず有機絶縁層を塗布。次に、発光ポリマーをパターンデータにしたがって滴下し有機絶縁膜を溶解させることによって自己整合隔壁を形成する仕組み。有機絶縁膜にはPMMA(ポリメチルメタクリレート)などを使用。発光ポリマーインクの溶剤には有機絶縁膜材料が溶解するクロロホルムやテトラリンを用いる。これにより、自己整合隔壁を自動的にパターニングする。このため、従来のバンクや発光ポリマーIJ印刷時のアライメントが不要となる。 最大の問題は、有機溶媒に溶解した樹脂が完全に分解せず発光ポリマーと反応して純度が低下したり、有機溶媒が残った隔壁に侵入して残留する懸念があること。もちろん、これは発光特性やライフタイムの低下を意味する。こうした疑問について開発者からは明確なアンサーがない。さらに、この工法はRGBフルカラーパネルに適用する場合、IJ印刷時にはRGBそれぞれのノズルを設けたヘッドを用いてRGBパターンを一括印刷する必要がある。つまり、従来のようにR、G、Bそれぞれの専用のマシンでIJ印刷することは位置合わせから考えると非常に困難である。また、RGB一括印刷時もインクの着弾精度や流動性を考慮したマージンを設ける、つまりピッチを広くする必要があると考えられる。このため、モノカラーパネル、エリアカラーパネル、低精細のカラーパネルに適用が限定されると考えられ、決して筋のいい自己整合技術にはみえない。 有機トランジスタでは自己整合技術を多用 有機トランジスタはエレクトロニクスデバイスのなかでももっとも自己整合技術を多用するといっていい。代表的なのは、下地を撥水性と親水性へ表面改質し、親水部へ各種インクを自己整合的に付着させたり、SAM(Self Assembled Monolayers)がある撥水部にペンタセンなどの有機半導体分子を自己整合的に成長・配向させる方法である。 こうした基本コンセプトをさらに改良したのが、日立製作所が考案したセルフアラインプロセス。図4のように、まずAu、Al-Nd、Cr、Taといった無機メタルを真空成膜し、フォトリソでパターニングする。このゲートパターンが後述するマスキングの役割を果たす。次に、SiO2やPVP(ポリビニルフェノール)などを成膜またはウェットコートしてゲート絶縁膜を形成する。次の工程が単分子膜(SAM)形成工程で、まずスピンコーティング、スリットコーティング、ディップコーティングといったウェットコーティング法で光分解型SAM材料を塗布し、100~200℃×5~10minで乾燥する。その後、基板の下側からUV光を照射し、UV光が当たった部分を分解・除去する。つまり、ゲートパターンをマスクにしてアライメントフリーでパターニングする。この結果、ゲート上に相当する部分だけにSAMが残る。続いて、ソース/ドレインとしてナノAgインクなどをIJ法や各種印刷法でラフに、つまりチャネル上に塗布する。SAMには撥水性があるため、それ以外の部分にメタルインクが付着する。その後、150~200℃×10minで焼成する。なお、ドレインと違い、ソースはマトリクス状にパターニングする必要があるため、この工程ではIJ法などである程度の精度でパターニングする必要がある。その後、ペンタセンをはじめとする有機半導体材料を成膜する。この際、有機半導体をチャネル部近辺に付着させる必要があるため、通常のペンタセンはメタルマスクスルー蒸着法、P3HT(ポリ-3-ヘキシルチオフェン)などの塗布型半導体材料はIJ法などでチャネル上に成膜する。この結果、SAM上で有機半導体材料はグレインサイズが大きくなるとともに、分子が板状に配向する。また、有機半導体はSAMの上でしか成長または配向せず、ソース~ドレイン間にセルフパターニングされる。ソース/ドレインの上部には配向・成長していない有機半導体材料がそのまま残るが、SAM上の有機半導体に比べ特性がきわめてプアーであるため、実質的には半導体層の役目を果たさない。 いうまでもなく、この工法の最大の特徴はフォトリソで精度よくパターニングしたゲートメタルをマスキングに用いる点で、この結果、それぞれの実基板のゲートパターンに合ったリアルタイムのアライメントがアライメントフリーで実現する。とくにプロセス中に寸法が変動しやすいプラスチックフィルム基板デバイスに有効で、筋のいい自己整合技術の代表といえる。

フォトマスクと同じで精度で凹版を

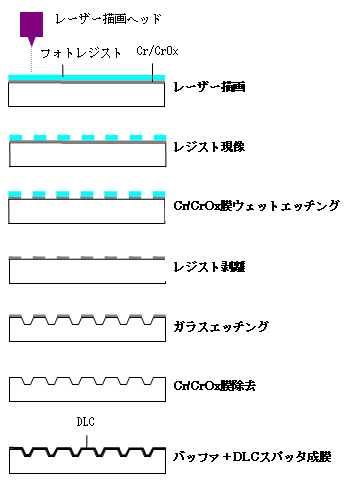

デバイス以外では、進映社などが考案したグラビアオフセット印刷用ハイブリッド凹版も自己整合理論を有効活用したプロダクトといえる。ハイブリッド凹版は従来のガラス製平版やメタル製平版のウィークポイントを解消した画期的な平版で、そのアドバンテージは製造フローからみるとわかりやすい。 図5のように、まずCr/CrOx膜+ポジ型フォトレジスト膜付きガラス基板(クロムマスクブランクス)上のフォトレジスト膜をレーザー描画した後、レジスト現像~Cr/CrOxウェットエッチング~レジスト剥離といったフローで原版を作製する。すなわち、ハードクロムマスクとまったく同じフローで作製する。次に、Cr/CrOxパターンをマスキングパターンにしてHFでガラス原版をウェットエッチング処理する。ガラスエッチング完了後、エッチャントを硝酸第二セリウムに置換しCr/CrOxパターンを除去する。これにより、ガラス製凹版が完成する。 これだけでもオフセット印刷用の凹版として使用できるが、周知のようにガラス製版はインクを凹版に埋め込んだ後のドクタースキージング(掻き取り)によって傷がつきやすく、チッピングも発生しやすい。とくに、PDP用Agペーストのようなガラスフリットを含有するインクでは傷の発生が避けられない。そこで、保護膜をコーティングする。具体的には、まずバッファ層として薄膜メタルをスパッタリング成膜。続いて、DLC膜をスパッタ成膜する。この結果、表面硬度1500Hv以上を実現。ドクタースキージングによっても傷がつきにくく、1万回以上の連続印刷が可能になる。 そのプロセスフローからわかるようにハイプレシジョンで凹パターンを作製できる。つまり、高精度レーザー描画装置で作製した原版をそのままガラスエッチングのマスキングに用いるため、版作製時における原版と凹版の寸法ずれがない。もちろん、実際にはガラスエッチングのXY精度は完全に原版通りとはいかないが、あらかじめ条件出しによってその傾向を把握し原版データにキャリブレーションしておけば前記の超大型サイズで寸法精度は±1μmに収まる。つまり、フォトマスクとほぼ同じプレシジョンが実現するわけである。 コストダウンできても特性を低下させることは許されない 最後に何が言いたいのかというと第1回と同じで、デバイスの特性・デザインルールや構造物に合った工法を採用すべきということである。自己整合プロセス技術といえば総じて聞こえはいいが、そのなかにはgood ideaもあれば、首をかしげたくなるideaもある。当たり前の話だが、製造プロセスはあくまでも“手段”であって、“目的”ではない。デバイスの特性を低下させる危険があるプロセス技術は基本的に価値がないのではないだろうか。 |

|||||

Private View 第1回 |

||||||

FPD製造プロセスでは常に新たな工法が提案され、一部は数年にわたる評価を経て量産採用される。コーナータイトル通り、ここではこれまでなかなか指摘できなかった辛口の私見でニューメソッドのメリット・デメリットを考えてみたい。もちろん、具体的な工法を例として挙げるため、不快に思う開発担当者・読者もいるだろう。その点についてはPrivate Viewということで許容していただければと思う。また、反論やコメント等があればこのメールアドレス宛て(info@stellacorp.co.jp)に意見をよせていただければ幸いである。第1回はポストフォトリソとして脚光を浴びるプリンティングテクノロジーについて考えてみたい。 一口にプリンティングテクノロジーといってもインクジェットプリンティング(IJ)法、スクリーン印刷法、凹版印刷法、凸版印刷法、グラビア印刷法、マイクロコンタクトプリント法などさまざまな方式があるのはいうまでない。近年、これら各種印刷法はFPD製造プロセスでリーズナブルなニューメソッドとしてプロポーザルが活発になっている。もちろん、その狙いはフォトリソの代替だ。そのメリットは総じて工程数削減と材料使用量削減によるコストダウン、そしてこれに付随するエコロジーだろう。確かに既存のフォトリソ工法を印刷法だけでリプレースするのが理想だ。しかし、実際にはリプレースにトライすると、①デバイスの設計マージンの縮小、②歩留まりの低下、③新規導入装置の安定性低下、といった問題に直面するだろう。もちろん、これらはニューメソッドを導入する際の当たり前のプロブレムで、いまさらここで指摘するまでもない。 IJ法は優れた工法だが、制約が多すぎる!! 辛口コーナーとしてここで言いたいのは、ニューメソッドを提案することに固執してデバイスに新たな負荷をかけるケースが多々みられることだ。これは、とくにIJ法で顕著なように感じる。

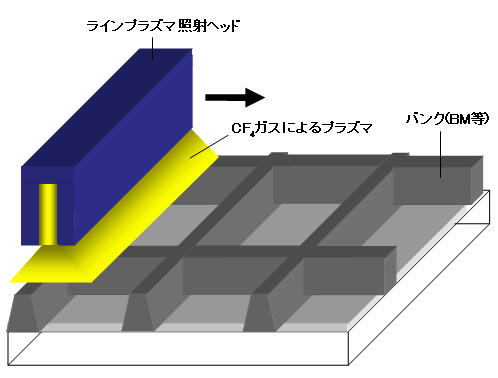

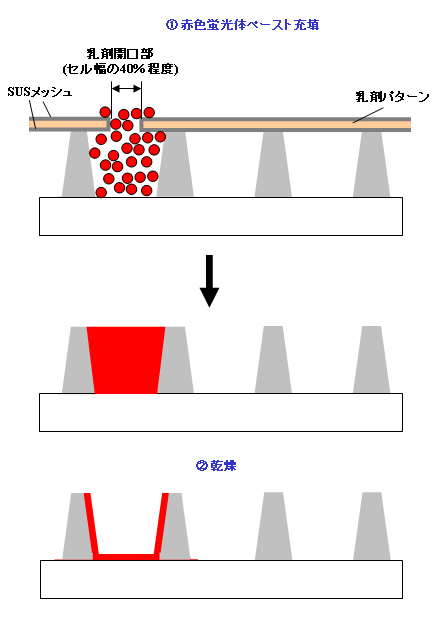

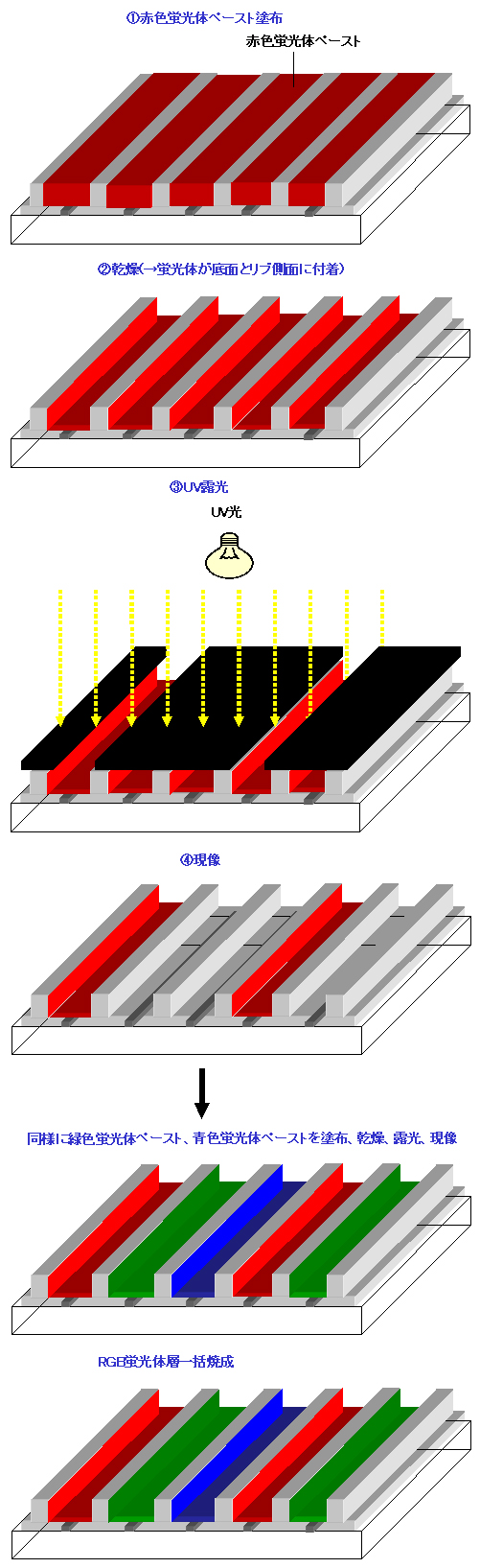

いまさらいうまでもないが、ここにきて産業用途にも採用されはじめたIJ法は素晴らしい工法である。なぜ長年、プリンター用途にしか採用されてこなかったのが不思議に思うほどだ。その長所は、①版レスのオンデマンド印刷、②基板や下地に非接触でインクを滴下するためダメージレス、の2点に尽きるだろう。こうした絶対的なアドバンテージを武器にFPD製造プロセスでも採用または採用の検討が進んでいるが、実際に量産プロセスに採用するに当たっては制約が多すぎる。 例えばLCDのカラーフィルター(CF)着色層や白色EL+CF方式有機ELディスプレイのCFに適用するケース。あらかじめマトリクス状に形成した隔壁(ブラックマトリクス)の溝のなかにIJ法でインクを充填するが、IJノズルからの着弾精度を補完するため、これら隔壁を大気圧プラズマまたは減圧プラズマなどで撥水処理するのが一般的だ。これによって、隔壁側壁に着弾したインクを溝のなかに流動させるという考え方だ。さらに、場合によっては下地を逆に親水化処理してインクのレベリング性を高める場合も多い。これらのプリトリートメントをしないとパターニング精度は大幅に低下し歩留まりが大きく低下したり、インクが底面で十分にレベリングしないため輝度が低下したり、輝度ユニフォミティが低下したりする。つまり、隔壁の撥水処理&下地の親水処理という余計な作業が入る。ただ、これらの2例は隔壁が本来必要という性格からまだましといえる。例えば有機トランジスタのソース/ドレイン形成にIJ法を用いる場合、感光性ポリイミドやネガ型フォトレジストをフォトリソで形成しておき、その後、IJ法でPEDOT/PSSインクを隔壁のない部分に滴下するといったケースもある。この場合、隔壁形成&表面改質というプロセスが新たに加わり、なんのためにソース/ドレイン形成工程を既存のフォトリソからリプレースしているのかわからなくなってしまう。 もちろん、デバイスの解像度にもよるものの、FPD製造プロセスにIJ法を適用する場合、こうした余分な負荷がかかるのが実情だろう。こうした負荷を考えると、そのコストメリットは大幅に相殺され、既存のフォトリソ工法と変わらないようになってくる。敢えて難しいことにトライして、コスト・環境面でのメリットはわずかといった感じになる。 IJ法にまつわるおかしな提案はまだまだある。古い話で恐縮だが、以前、PDPの蛍光体層にIJ法を活用しようという動きがあった。この場合、ノズル目詰まりの懸念から、既存のミクロン蛍光体パウダーは使用できない。このため、新たに開発したナノ蛍光体パウダーを使用し、インク化してIJ滴下する仕組みだ。しかし、PDPの蛍光体層は膜厚10~15μmの厚膜である。ノズル径数十μmのIJ法ではバリアリブ内への充填に時間がかかる。さらに、これには異論反論もあると思うが、ナノ蛍光体はミクロン蛍光体に比べ相対表面積が大きくなるため、発光特性が低下する懸念があること。いうまでもなく、プラズマ放電で発生させた真空紫外光によって蛍光体は励起されるが、一般的にその表面は欠陥が多く発光にほとんど寄与しないためである。すなわち、この場合はデメリットばかりであり、もちろんこの話は提案だけに終わった。 ところで、PDPの蛍光体層形成工程にはスクリーン印刷法という非常にマッチした工法があり、従来から現在までスクリーン印刷法が量産採用されている(パナソニックを除く)。スクリーンマスクの乳剤開口部から蛍光体ペーストをリブ間の溝にフル充填し、乾燥によって固形成分を底面とリブ側壁に付着させる仕組みである。この際、有利なのは充填プロセスであるため、スクリーンマスクの乳剤開口幅を溝幅の40%程度に設定できることである。これによって多少スクリーンマスクと基板の相対位置がずれていても隣接するセルへ蛍光体ペーストが流れ込むことはない。すなわち、このプロセスは非常にマージンの高い工法といえる。しかし、ワイドVGAからワイドXGAへ、またワイドXGAからフルHDへ移行する際には必ずスクリーン印刷代替の議論があった。上記のIJ法もそうした一環である。 さらに、フォトリソにリプレースしようという筋の悪い提案もあった。蛍光体パウダーを感光性樹脂や溶剤などとともに感光性ペースト化または感光性フィルム化し、RGB蛍光体層をRGB3回のフォトリソで形成しようという発想だ。確かにフォトリソなので精度面での問題はない。しかし、この工法では2色目、3色目の感光性蛍光体ペースト塗布・充填または感光性蛍光体フィルムラミネート時に、1色目と2色目、3色目が混在してしまう。これを露光・現像によって1色目部分に付着した2色目、3色目の蛍光体を除去するのだが、その際に完全に除去できるのか、また1色目が現像によって除去される危険がないのかといった問題がある。また、感光性ペーストまたは感光性フィルムに用いられる感光性ポリマーは総じて低温では分解しないため、焼成工程で完全にバーンアウトできるかといったデメリットもあった。いうまでもなく、完全に除去できずに残留したバインダーはその後の排気工程やエージング工程に多大な負荷をかけ、最悪の場合はこれらの工程でも除去できず、パネル駆動中にアウトガスを発生してパネルのライフを低下させる。もちろん、こうした感光性工法はスクリーン印刷法に比べ製造コストが圧倒的に高い。つまり、“見た目”の精度以外、なにひとつ有利な点はなかったのである。このため、これら感光性工法は検討こそされるものの、量産採用には至らなかった。至極当然の話である。

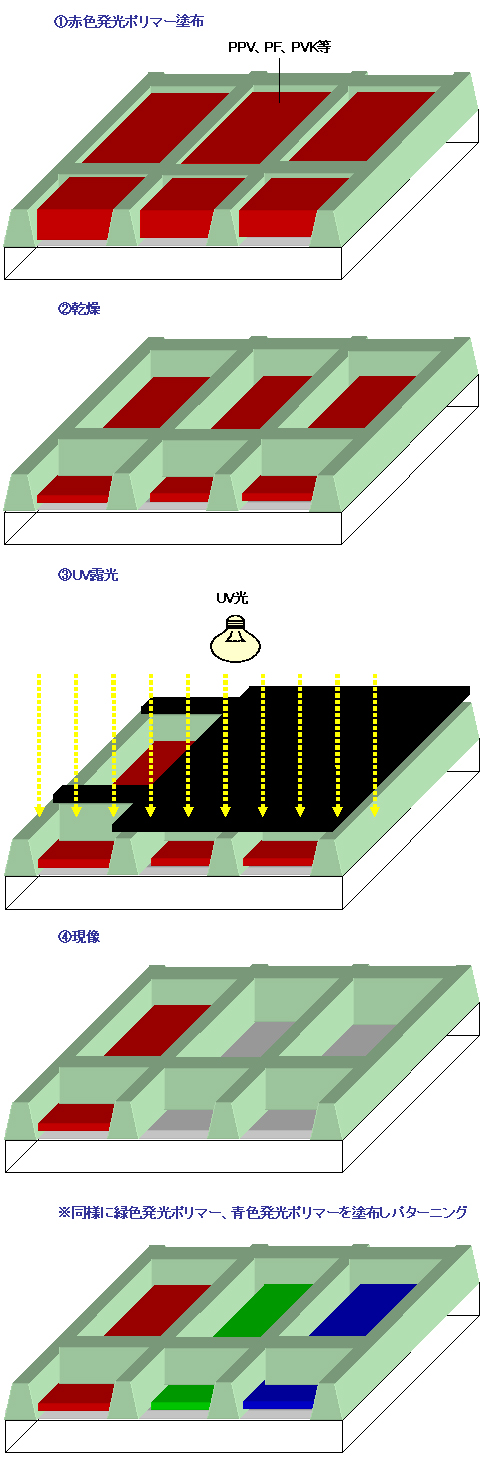

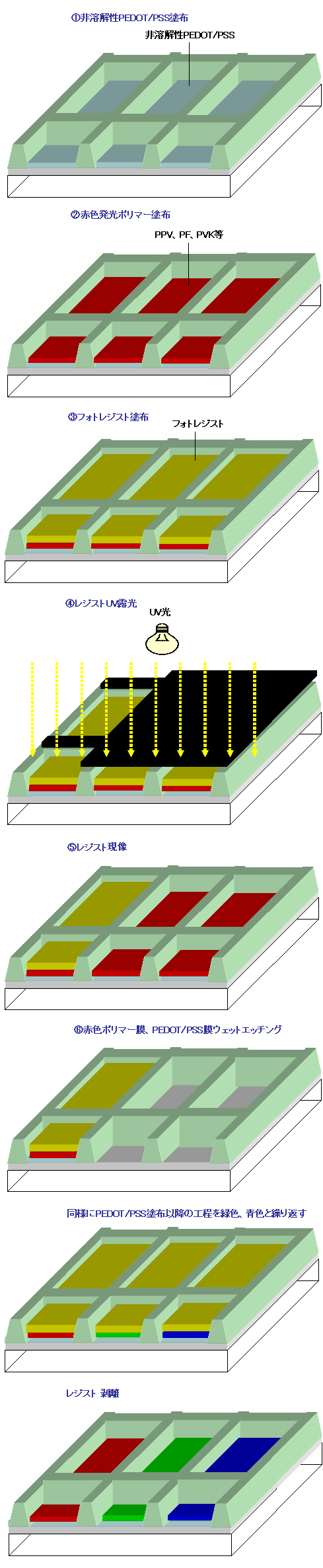

同様に、高分子有機ELDの発光層にフォトリソを用いるという提案もミスマッチに思える。これまでに提案されているフォトリソ工法は図4、5の二つで、プロセス①は1色目形成後、2色目、3色目の塗布・露光・現像工程で1色目がダメージを受ける可能性が排除できない。また、センシティブな有機発光材料に感光性ポリマーを添加するなど、本質的な特性が低下する傾向がある。他方、プロセス②は①の問題を緩和したものだが、やはり発光層ウェットエッチング時のダメージに疑問が残る。もちろん、これらフォトリソ工法は既存のIJ法に比べ大幅なコストアップをともなう。

何が言いたいのかというと、デバイスの特性・デザインや構造物に合った工法を採用すべきで、例えば“IJ法はアドバンストテクノロジーだから”、とか、“フォトリソは精度が高いから”という単純な理由だけで採用を検討すべきではないという点である。またIJ法に話を戻すが、IJ法を電極のパターニングに用いるという提案もある。これもデバイスや構造物によるものの、goodな工法には思えない。IJ法はその原理からそもそも“点”を撃つのに適した工法と思われ、電極のような“線”を描画するにはインクのレベリング性はもちろんのこと、液滴サイズ、液滴ピッチ、さらに滴下順などを最適化しなければならない。また、本来IJ法は厚膜化が不得手であるため、その導電性からミクロンオーダーの膜厚が要求される電極用途ではさらにマルチショット化や重ね撃ちといった工夫が必要になる。さらに、ノズル目詰まりの問題からナノメタルインクが必要になる。これに対し、スクリーン印刷をはじめとする印刷法(版を用いる印刷法)は総じて電極のような一定方向に配向するパターンが得意であり、処理速度もIJ法に比べ圧倒的に速い。もちろん、厚膜化もIJ法に比べ容易だし、高価なナノメタルペーストを使用する必要はない。 もちろん、FPD製造プロセスでIJ法や感光性工法がダメで、各種印刷法はいいといっているわけではない。しつこいようだが、そのデバイスや構造物に合った工法がベストチョイスになる。例えば、スクリーン印刷はその印刷メカニズムから超大型マザーガラスを用いたパターン印刷には適していない。線幅解像度は20~30μmまで可能だが、寸法精度は超大型マザーガラスでは±数十μmになってしまうからだ。一方、有機トランジスタのような比較的小型デバイスなら寸法精度±10μmは可能なため、電極用途などに十分使用できる。他方、チャネル上に形成する有機半導体層などの“点パターン”には適しておらず、このケースでは非接触でダメージレスのIJ法がベターということになる。 以上、多少支離滅裂になってしまったが、Private Viewの第1回はここでキーボードを打つのをやめる。今後もデバイスに合った工法という観点から私見を述べてみたい。なお、第2回は自己整合技術について考えてみたい。 |

||||||