|

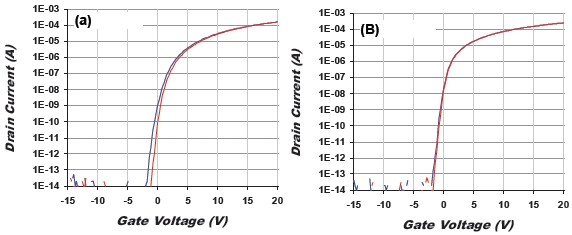

IDW'11�`�_����TFT�� |

||||||||||||||||||||||||||||||||||||||||||||

�v���Z�X����H�v���邾����IGZO-TFT�̓��������P

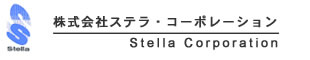

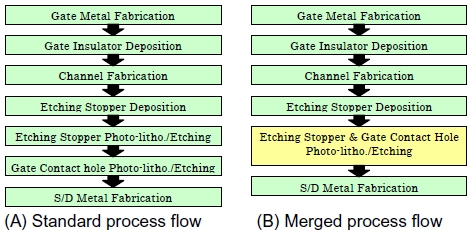

�@�܂��A�_����TFT�̉��҂Ƃ��Ă̒n�ʂ��m������a-IGZO(In-Ga-Zn-O)�ł͗ʎY���ڑO�ɔ����Ă��邱�Ƃ������Ă��A�f�o�C�X�M�����Ɋւ��锭�\���ڂɂ����B���������Ȃ��ALG Display�̓t�H�g���\�𑝂₳���Ƀv���Z�X�t���[���H�v���邱�Ƃɂ���ď����������M���������߂邱�Ƃɐ��������B �@���m�̂悤�ɁA�R���x���V���i���ȃ{�g���Q�[�g�^a-IGZO-TFT�ł̓\�[�X/�h���C���`�����̃t�H�g���\�H����t�H�g���W�X�g�����H���Ń`���l�����_���[�W����̂�h�����߁A�`���l���̏㕔�ɃG�b�`���O�X�g�b�p�[��݂���G�b�`���O�X�g�b�p�[�^�C�v���嗬�ƂȂ��Ă���B�������A���̍\���ł��`���l���ɋz������L�@�����ɂ��R���^�~�l�[�V�������܂������Ȃ��Ƃ͌�����Ȃ��B�����ŁAa-IGZO���ƃG�b�`���O�X�g�b�p�[��A���������ꊇ�p�^�[�j���O����v���Z�X���l�Ă����B �@����̌����ł�2200�~2500�o�̑�8����}�U�[�K���X���a-IGZO-TFT���쐻�����B�Q�[�g���^����Cu�����X�p�b�^�����O�����A�Q�[�g�≏����SiO2�����v���Y�}CVD�����Ba-IGZO���͖���60nm�Ŏ����X�p�b�^�����O���������B�����āASiO2�G�b�`���O�X�g�b�p�[���v���Y�}CVD����������ACu�����X�p�b�^�����O�������ă\�[�X/�h���C�����`���B�Ō�ɁASiO2�p�b�V�x�[�V������300nm�Ńv���Y�}CVD���������B�`���l������11.4��m�A�`���l������100��m�ł���B �@�}1�̂悤�ɁA�X�^���_�[�h�v���Z�X��a-IGZO���𐬖����t�H�g���\�Ńp�^�[�j���O������A�G�b�`���O�X�g�b�p�[�𐬖����t�H�g���\�Ńp�^�[�j���O����B����A���ǃv���Z�X��a-IGZO���ƃG�b�`�X�g�b�p�[����A���������t�H�g���\�ňꊇ�p�^�[�j���O������A�\�[�X/�h���C���Ƃ̃R���^�N�g�̈���m�ۂ��邽�߁A�G�b�`���O�X�g�b�p�[�����ēx�t�H�g���\�Ńp�^�[�j���O���ă`���l���㕔�����Ɏc���B

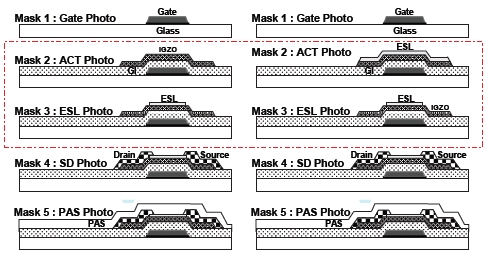

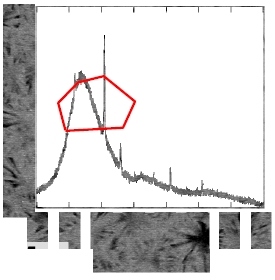

�@a-IGZO-TFT�쐻��A���FEL�{COA(�J���[�t�B���^�E�I���E�A���C)�����̃{�g���G�~�b�V�����^�L�@EL���`�������B��̓I�ɂ́ATFT���RGB��COA���`��������AITO��f�d�ɂ��`���B���̌�A�z�[���A���w�A�����w�A�d�q�A���w�A�J�\�[�h��^����������B �@�\1�̓X�^���_�[�h�v���Z�X�f�o�C�X�Ɖ��ǃv���Z�X�f�o�C�X�̓������r�������̂ŁA�h���C���d����10V�ɌŒ肵���ꍇ�A���ǃv���Z�X�f�o�C�X�̓��r���e�B��11.44cm2/V�s�AVth��1.24V�AON�d����111.24��A�AS�t�@�N�^�[��0.17V/dec�ƃX�^���_�[�h�v���Z�X�f�o�C�X�ɔ�חǍD�Ȓl������ꂽ�B����́A��L�̃v���Z�X�t���[����ꊇ�p�^�[�j���O���ɃG�b�`���O�X�g�b�p�[���`���l�����v���e�N�g���邱�Ƃ���Aa-IGZO�\�ʂɗL�@�R���^�~�l�[�V�������������Ȃ����߂ł���B�}2�̓X�^���_�[�h�v���Z�X�f�o�C�X��SIMS�[���v���t�@�C�����͌��ʂŁAa-IGZO�\�ʋߖT�ɃJ�[�{���R���̃s�[�N��������B�܂�Aa-IGZO���̃p�^�[�j���O���ɂ�����t�H�g���\�H����W�X�g�����H���ɂ���ăJ�[�{�����g�U���\�ʂ���������B

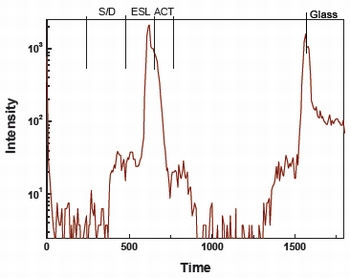

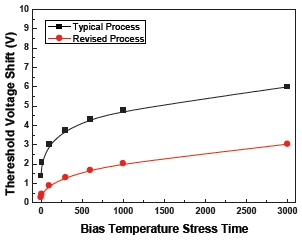

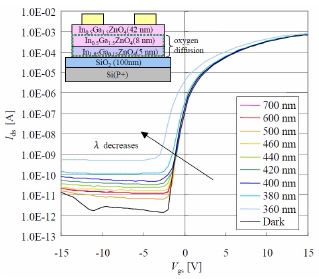

�@�}3�̓\�[�X/�h���C���d����10V�A�Q�[�g-�\�[�X�d�����|15�`�{20V�ɂ����ۂ̃g�����X�t�@�[�����ŁA���ǃv���Z�X�f�o�C�X�̓d���̓h���C���d��1nA��0.05V�������B����́A0.36V�������X�^���_�[�h�v���Z�X�f�o�C�X�ɔ�\���������A�q�X�e���V�X�����������Ƃ��킩��B�܂�Aa-IGZO-TFT�̓d�C�����͊����w�ƃG�b�`�X�g�b�p�[�E�ʂ̏�Ԃɋ����ˑ�����킯�ł���B �@���̏o�͓��������肵���Ƃ���A���ǃv���Z�X�f�o�C�X�̃\�[�X/�h���C���d���̓X�^���_�[�h�v���Z�X�f�o�C�X�������������B�}4��60����30V�̃|�W�e�B�u�o�C�A�X��3000�b��������ۂ�Vth�ϓ��������BVth�V�t�g�͉��ǃv���Z�X�f�o�C�X��2.76V�������̂ɑ��A�X�^���_�[�h�v���Z�X�f�o�C�X�͂���2�{���x�������B �@�Q�l�Ƃ��āA�ʐ^1�ɏ�L�̉��ǃv���Z�X�ō쐻����a-IGZO-TFT�쓮��31�^�L�@ELD�������B�Ȃ��A�T�u�s�N�Z����H�͐���TFT��2�L���p�V�^�ō\�������B IGZO�����X�^�b�N���Č��Ǝˎ���Vth�V�t�g��}�� �@����A�x�m�t�C�����͐��E�ō��N���X�̃n�C���r���e�B������A����a-IGZO-TFT�ɂƂ��ėB��̎�_�Ƃ������Ǝˎ��ɂ���������ϓ������������f�o�C�X������B���m�̂悤�ɁA���Ǝˊ����ł�a-Si TFT�قǂł͂Ȃ����̂́Aa-IGZO-TFT����r�I�傫��Vth�V�t�g���ϑ������B���̂����Ȍ����Ƃ��ẮA�`���l���`�Q�[�g�≏���E�ʂɎ_�f�������������邽�߂Ƃ�����B�����ŁA�f�o�C�X�\�����H�v���邱�Ƃł��̖����������邱�Ƃɂ����B �@�܂��AIn:Ga:Zn��1:1:1�g����a-IGZO���𐬖����A�j�[��������A�_�f�g�U�[���ׂ��BSIMS���͂̌��ʁA�A�j�[�����x��350���ȏ�ɂȂ�Ɩ�����_�f�g�U���N����A450���ł͎_�f�g�U�[����15nm�ɒB���邱�Ƃ��킩�����B�����ŁA���̎_�f�g�U�������ĐϋɓI�ɗ��p����f�o�C�X�\�����l�Ă����B �@����f�o�C�X�́A�܂��M�_��SiO2��(����100nm)�t���V���R���E�F�n�[���In1.85Ga0.15ZnO4����5nm�A�����đ�1�ϔM���C���[�Ƃ���In0.5Ga0.15ZnO4����Xnm�Ń}�O�l�g�����X�p�b�^�����O���������BX������8nm(TFT-A)��50nm(TFT-B)�ɂ����B���̌�AO2���͋C�ɂ�����450���ŃA�j�[���B����ɁATFT-A�͑�2�ϔM���C���[�Ƃ���In0.5Ga0.15ZnO4����50-Xnm�Ő��������B�����āATi/Au(10nm/40nm)�������^���}�X�N�z���ɃX�p�b�^�����O�������ă\�[�X/�h���C�����_�C���N�g�`���B�Ō�ɁA�I�[�~�b�N�R���^�N�g�����m�ۂ��邽�߁AO2���͋C�ɂ�����450���ŃA�j�[�������B

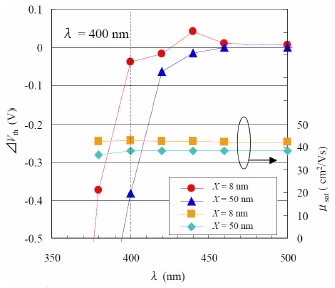

�@���Ǝˉ��ɂ����鉞������]�����邽�߁AXe�����v����360�`700nm�̌����Ɠx100��W/cm2�ŏƎˁB���̍ہA�g�����X�t�@�[�����̓_�[�N��ԂƏƎˌ�̒l�𑪒肵���B �@�}5��TFT-A��Vgs-Ids�����������B�_�[�N��Ԃł�TFT-A��41.8cm2/V�s�ATFT-B��38.4cm2/V�s�ƂƂ��ɍő�̃��r���e�B���������B�܂��A�}6-�E���̂悤�ɂǂ�����������Ǝ˂��Ă����r���e�B�͂قƂ�Ǖω����Ȃ������B �@����AVth�͌��Ǝ˂ɂ���Đ}6-�����̂悤�ɑ傫���ω������B��̓I�ɂ́A�ǂ���̃f�o�C�X�Ƃ��Ǝ˔g����440nm�ȏ�ł͂قƂ�Ǖω����Ȃ��������A400nm�ȉ��ɂȂ�Ƒ傫�ȈႢ���݂��A400nm�ł�TFT-A�͂킸��0.04V�����V�t�g���Ȃ������̂ɑ��ATFT-B��0.38V���V�t�g�����B �@���������Ⴂ�͎_�f�g�U���ʂɂ��ƍl������B�܂�AX��8nm�ł���TFT-A�ł�450���ŃA�j�[������Ǝ_�f�g�U���[��15nm�ɂ܂ŒB���邽�߁AIn1.85Ga0.15ZnO4�`���l���̃o���N�̈�ɂ����錇�ׂ�In0.5Ga1.5ZnO4�ϔM���C���[�Ƃ̊E�ʂŎ_�f���q�ɂ���đ��E����邩��ł���B���̌��ʁATFT-B�ɔ���ז��x���Ⴍ�Ȃ�B���������āAVth�V�t�g���}�������킯�ł���B�܂�A���̃f�o�C�X�\���Ȃ�n�C���r���e�B���ێ������܂܁A���Ǝˊ��ł�Vth�V�t�g���}���ł���B ��������N���p�[�W����a-IGZO:H��

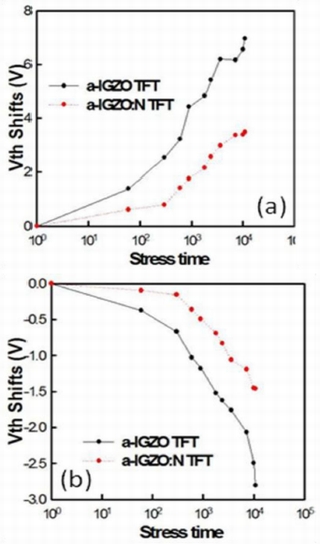

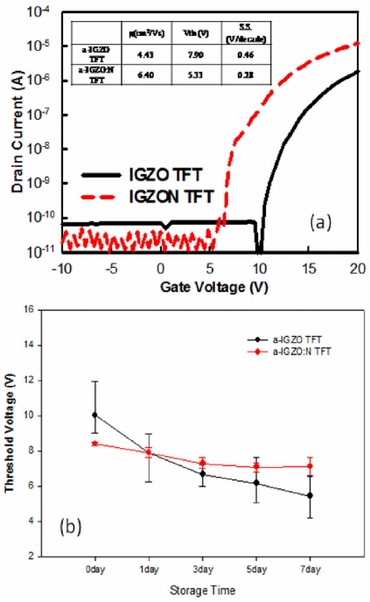

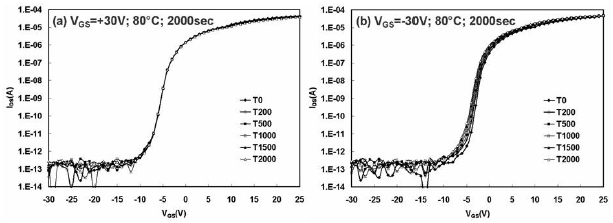

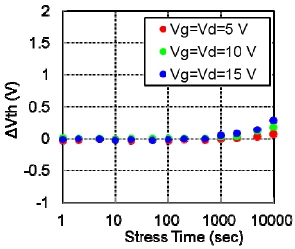

�@��p��National Chiao Tung University���AVth�V�t�g�}���Ƃ����ϓ_����a-IGZO��N���h�[�v����Ƃ����V���v���ȕ��@���Љ���B���_����q�ׂ�ƃo�C�A�X�X�g���X�e�X�g����Ǝˊ���Vth�V�t�g���}���ł��������łȂ��A���r���e�B���͂��߂Ƃ���C�j�V�������������シ��Ƃ����B �@�����ł́A�V���R���E�F�n�[���Ƀ{�g���Q�[�g�^�f�o�C�X���쐻�����B�܂��A650���ŃA�j�[�����Ċ�\�ʂɔM�_��SiO2�����`�����Q�[�g�@�\��t�^�B�����āAIn:Ga:Zn:O(1:1:1:4)�y���b�g��p����a-IGZO���������A�p���[100W�A����5�~10-3torr�Ń��A�N�e�B�u�X�p�b�^�����O���������B������50nm�ł���B���̍ہAAr�K�X(10sccm)�ɉ����AN�K�X�𗬗�2sccm�Ńp�[�W�����B���̌��ʁA�����w��a-IGZO:N�ɂȂ�B�Ȃ��A�X�p�b�^�����O�����̓��^���}�X�N����čs�������߁A�t�H�g���\�ɂ��p�^�[�j���O�͕s�v�ł���B�����āAITO����50nm�ŃX�p�b�^�����O�������A�\�[�X/�h���C���Ƃ��ăp�^�[�j���O�B�Ō�ɁA350���~1���ԃA�j�[�������B �@�}7-(a)�Ɏ���f�o�C�X�̃g�����X�t�@�[�����������B���r���e�B��a-IGZO TFT��4.43cm2/V�s�Aa-IGZO:N TFT��6.4cm2/V�s�ŁAVth�AS�t�@�N�^�[�Ƃ���҂̕����Ⴂ�l���������B�܂��A�f�o�C�X���C���ɕ��u���ē����ϓ���]�������Ƃ���A�}7-(b)�̂悤��Vth�V�t�g��a-IGZO TFT��2.23V�Aa-IGZO:N TFT��1.28V�������B����ɁAa-IGZO:N TFT�͎��Ԃ̌o�߂ƂƂ���Vth�V�t�g�ʂ��ɂ₩�ɂȂ����B �@�}8-(a)�̓|�W�e�B�u�o�C�A�X�A(b)�̓l�K�e�B�u�o�C�A�X��104�b��������ۂ�Vth�����ŁAa-IGZO TFT��Vth�V�t�g�͑O�҂�6.96V�A��҂Ł|2.8V�������B����ɑ��Aa-IGZO:N TFT��Vth�V�t�g�͑O�҂�2.97V�A��҂Ł|1.7V�������B����́A�O�����ɓ݊���N���p�[�W���邱�Ƃɂ����a-IGZO�����ɂ�����_�f���q�̋z����E�����}������邽�߂ƍl������B�܂�Aa-IGZO:N TFT�͐M�����̖ʂł��D��Ă���Ƃ�����B

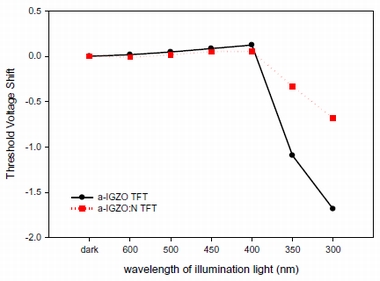

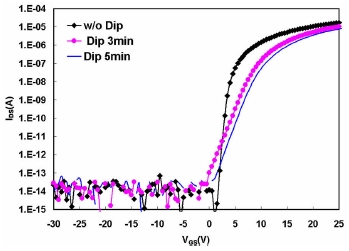

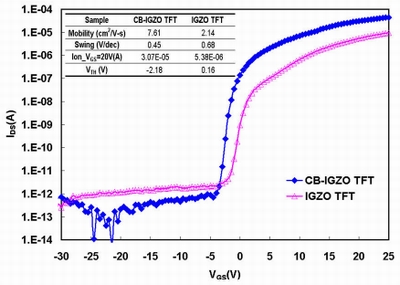

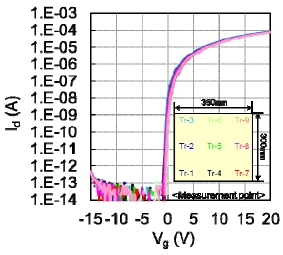

�@�}9�͔g��300�`600nm�̌����Ǝ˂����ۂ�Vth�V�t�g�ŁA���f�o�C�X�Ƃ��Ǝ˔g����400�`600nm�̏ꍇ�AVth�͂قƂ�Ǖϓ����Ȃ��������A350nm�ȉ���UV�g���ɂȂ��Vth�V�t�g���傫���Ȃ����B�������A���̏ꍇ�ł�a-IGZO:N TFT��Vth�V�t�g��a-IGZO TFT��菭�Ȃ������B �`���l���ւ�Cu�g�U��}������IGZO-TFT�̈��萫�����P �@AU Optronics�́Aa-IGZO TFT�Ń\�[�X�E�h���C����Cu��p�����ۂɖ��ƂȂ�`���l���ւ�Cu�g�U��}��������@������B �@����f�o�C�X�́A�@Cu���𐬖����Q�[�g���`���A�ASiNx�����v���Y�}CVD�������Q�[�g�≏�����`���A�Ba-IGZO����DC�X�p�b�^�����O�������_���������̑w���`���A�CSiOx�����v���Y�}CVD�������G�b�`���O�X�g�b�p�[���`���A�DCu���𐬖����\�[�X/�h���C�����`���A�ECu�̊g�U��}������Cu�u���b�N(CB)�v���Z�X��lj��A�FSiOx���𐬖����p�b�V�x�[�V�������`���A�Ƃ������t���[�ō쐻�B�Ō��N2���͋C�ŃA�j�[�����������B�����ŇE��CB�v���Z�X��K�p�����f�o�C�X��CB-IGZO TFT�ACB�v���Z�X���X�L�b�v�����f�o�C�X��IGZO-TFT�ƌĂԂ��Ƃɂ���B�Ȃ��A�C�ɂȂ�CB�v���Z�X�̏ڍׂɂ��Ă͖��炩�ɂ��Ă��Ȃ��B �@�}10��VDs��10V�������IDs-VGs�����ŁAIGZO-TFT��S�t�@�N�^�[��0.45Vdec����0.67V/dec�֗B�܂��AVGS��20V�ł�ON�d����83���Ɍ�������ƂƂ��ɁAVth���|2.17V����0.15V�փV�t�g�����B����́A�\�[�X/�h���C������Cu���`���l���֊g�U�������߂ƍl������B

�@��������Cu�g�U�ɂ��e���������邽�߁A�Q�[�g�ƃ\�[�X/�h���C����Al����p����ƂƂ���CuSO4(�Z�x0.05mol)�n�t�ŐZ�Ђ������t�@�����X�f�o�C�X���쐻�����B�}11�͂���IDs-VGs�����ŁACu���g�U����Ɠ��������邱�Ƃ��킩��B �@�}12�̓f�o�C�X��80���ɉ��M���Q�[�g�Ɂ{30V�A�|30V�̃o�C�A�X�X�g���X��2000�b��������o�C�A�X�X�g���X�e�X�g���ʂŁACB-IGZO TFT��Vth�́{30V�������0.07V�A�|30V�������1.01V�V�t�g�����ɉ߂��Ȃ������B IGZO-TFT�ɋ��͂ȃ��C�o�����o�� �@a-IGZO�ȊO�̎_����TFT�ł́A�Ȃ�Ƃ����Ă��\�j�[��IGO(In-Ga-O)TFT�����ڂ��W�߂��B���_�����ɂ����ƁA���̃C�j�V���������E���萫�Ƃ�a-IGZO-TFT�����̂����x���ŁA�g�_����TFT��a-IGZO-TFT�h�Ƃ�������܂ł̏펯���\�����犴���������B

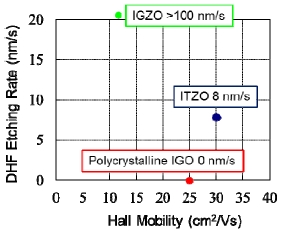

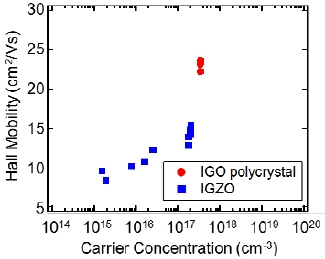

�@���m�̂悤�ɁAIGZO����Zn��In2O3�̌�������}����������AGa�͂��̋��������G�l���M�[�ɂ����O�����艻������������ʂ����B���̂��߁AZn���X��IGO�͐M��������������ȑ����������̂ɂȂ�Ɨ\�z�����B �@��̓I�ɂ�a-IGZO�ɔ�ׁA�@�������Ȃ̂�HF�����ł��G�b�`���O����Ȃ��A�A�z�[�����r���e�B�������v���Z�X�}�[�W�����L���A�Ƃ��������b�g������B�}13�̓L�����A���x�ƃz�[�����r���e�B�̊W�ŁAa-IGZO�͐�������O2������������ƃz�[�����r���e�B��10cm2/V�s����15cm2/V�s�֑�������B����A������IGO��O2�������͂��߂Ƃ��鐬�������Ɋւ�炸a-IGZO���������z�[�����r���e�B��������B�}14�̓z�[�����r���e�B��DHF(0.5��)�ɂ��G�b�`���O���[�g�̊W�ŁA������IGO�͍������r���e�B���ێ������܂�DHF�ɑ������σG�b�`���O�����������B �@�ʐ^2�ɏo�����Y��IGO�^�[�Q�b�g��p���Đ�������IGO���̏�ʐ}�������B�O���C���͐��Snm�T�C�Y�̒���T�u�O���C�����A�Ȃ������b�h���C�N�\���ŁA���̃T�C�Y��2��m���x�ł���B���������T�u�O���C���`���ITO(In2O3-SnO2)�ł��ϑ������B

�@�Ƃ���ŁAZnO�̏ꍇ�A�O���C���o�E���_���[�Ɍ��ׂ�����ƃL�����A�`�����j�Q�����B���̂��߁AZnO�ł͖����ɔ�Ⴕ�ăO���C���T�C�Y���������A���ʓI�Ƀz�[�����r���e�B���ቺ����B �@����ɑ��AIGO�͖���50nm�ł�25cm2/V�s�ƍ����z�[�����r���e�B���ێ�����B����́AZnO��In2O3�̌������̈Ⴂ�ɂ��B�܂�AZnO�̓E���c�^�����AIGO�͓S�}���K���z�^�����ł���A�O�҂ɔ�בΏ̐����Ⴂ����ł���B�����������R����IGO-TFT��L�@ELD�̃o�b�N�v���[���ɗp���邱�Ƃɂ����B �@����f�o�C�X�̓G�b�`���O�X�g�b�p�[�t���{�g���Q�[�g�\�����̗p�B�������A�}15-(a)�̂悤�ɃX�^���_�[�h�v���Z�X�͍H�����������A�f�o�C�X�����[�R�X�g�Ő�������̂�����B�����ŁA�}15-(b)�̂悤��SiO2�����G�b�`���O�X�g�b�p�[�ƃQ�[�g�≏���ɗp����BHF�ňꊇ�G�b�`���O���A�G�b�`���O�X�g�b�p�[�ƃQ�[�g�R���^�N�g�z�[�����ꊇ�p�^�[�j���O���邱�Ƃɂ����B�����܂ł��Ȃ��A���̃v���Z�X��IGO�ɍ����σG�b�`���O�������邩��K�p�ł���킯�ł���B���Ȃ݂ɁAa-Si TFT�ŃX�^���_�[�h�ƂȂ��Ă���o�b�N�`���l���\���f�o�C�X���쐻�������A�G�b�`���O�X�g�b�p�[���X�̂��߁A�M�����A���j�t�H�~�e�B�Ƃ��f�B�X�v���C�pTFT�Ƃ��Ă͕s�\���������B

�@�}16�͑�1����}�U�[�K���X(300�~350mm)��ɍ쐻����IGO-TFT�̃g�����X�t�@�[�����ŁA���r���e�B��23.8cm2/V�s�AVth�́|0.1V�AS�t�@�N�^�[��0.30V/dec�������B�܂��A�}�U�[�K���X�S��ɂ����郂�r���e�B�ψꐫ�́}0.86cm2/V�s�������B �@�}17��50����Vg��5�`15V�AVd��5�`15V��1���b��������|�W�e�B�u�o�C�A�X�X�g���X�e�X�g���ʂŁAVth�V�t�g�͂킸��0.3V�ɉ߂��Ȃ������B�����������ʂ́A�v���Z�X���Ń`���l���ƃ\�[�X/�h���C���̃R���^�N�g�̈�ő傫�ȃ_���[�W���Ȃ����߂ƍl������B �@�ʐ^3��IGO-TFT�쓮9.9�^�L�@ELD(960�~540��f)�̕\����ŁA�V���v����2TFT�{1�L���p�V�^�\���ŋ쓮�����邱�Ƃ��ł����B

�Q�l����

|

||||||||||||||||||||||||||||||||||||||||||||