|

STELLA’تگM‚ح‡ٹƒXƒeƒ‰پEƒRپ[ƒ|ƒŒپ[ƒVƒ‡ƒ“‚ھ‰^‰c‚µ‚ؤ‚¢‚ـ‚·پB |

SID 11پ`—L‹@EL•ز |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

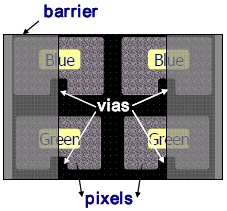

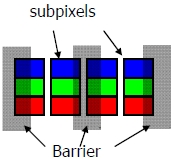

پ@‹ك”NپA’چ–ع“xNo.1‚ئ‚ب‚ء‚ؤ‚¢‚é3DƒfƒBƒXƒvƒŒƒC‚إ‚حپASamsung Mobile Display‚ھƒ‚ƒoƒCƒ‹‹@ٹي—pƒOƒ‰ƒXƒtƒٹپ[—L‹@ELD‚ة‚آ‚¢‚ؤ”•\‚µ‚½پB پ@ژü’m‚ج‚و‚¤‚ةپAƒOƒ‰ƒXƒtƒٹپ[3D•ûژ®‚جƒپƒWƒƒپ[ƒپƒ\ƒbƒh‚ئ‚¢‚¦‚éƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒA•ûژ®‚ح‰tڈ»ƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒA‚ً—p‚¢‚é‚ج‚ھˆê”ت“I‚إ‚ ‚éپB’تڈي‚ج2D•\ژ¦‚à—eˆص‚ب‚½‚ك‚¾‚ھپA‰tڈ»ƒZƒ‹‚ة‰ء‚¦•خŒُƒtƒBƒ‹ƒ€‚ھ•K—v‚ب‚اگ»‘¢ƒRƒXƒg‚حŒˆ‚µ‚ؤˆہ‚‚ب‚¢پB‚ـ‚½پAژصŒُƒoƒٹƒA‚ًگف‚¯‚錴—‚©‚ç3D•\ژ¦ژ‚جگ…•½‰ً‘œ“x‚ح”¼•ھ‚ة‚ب‚éپB‚»‚±‚إپA‰tڈ»ƒoƒٹƒA‚ً—p‚¢‚ب‚¢گV‚½‚بƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒA‚ئƒTƒuƒsƒNƒZƒ‹”z—ٌ‚ًچlˆؤ‚µ‚½پB پ@گ}1‚ةƒTƒuƒsƒNƒZƒ‹”z—ٌ‚ًژ¦‚·پBƒsƒNƒZƒ‹‚حکZ‚آ‚جƒTƒuƒsƒNƒZƒ‹‚©‚ç‚ب‚èپA3D•\ژ¦ژ‚àگ…•½‰ً‘œ“x‚ھ’ل‰؛‚·‚邱‚ئ‚ح‚ب‚¢پB‚½‚¾‚µپA‚±‚جƒfƒUƒCƒ“‚إ‚حچ¶–ع—p‚ئ‰E–ع—p‚ج‹P“x‚ًƒoƒ‰ƒ“ƒX‚³‚¹‚邽‚كپAƒoƒٹƒAƒpƒ^پ[ƒ“‚ًگ³ٹm‚ةƒpƒ^پ[ƒjƒ“ƒO‚·‚é•K—v‚ھ‚ ‚éپB‚»‚±‚إپAگ}2‚ج‚و‚¤‚ةƒAƒmپ[ƒh‚ئƒRƒ“ƒ^ƒNƒg‚³‚¹‚éƒRƒ“ƒ^ƒNƒgƒzپ[ƒ‹‚ً‘خڈج”z—ٌ‚ة‚µ‚½پB‚±‚ê‚حپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒfƒUƒCƒ“‚ج‚و‚¤‚ةƒRƒ“ƒ^ƒNƒgƒzپ[ƒ‹‚ًƒTƒuƒsƒNƒZƒ‹‚ج’[‚ة”z’u‚·‚é‚ئپAچ¶‰E‚ج‹P“xƒoƒ‰ƒ“ƒX‚ً‚ئ‚é‚ج‚ھ“‚‚ب‚邽‚كپB

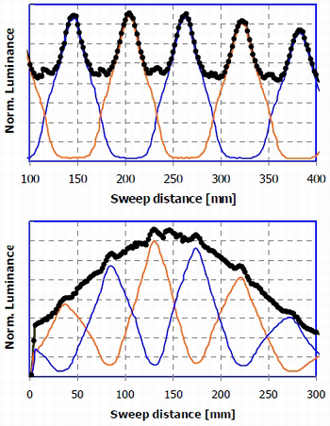

پ@“¯ژذ‚حڈم‹L‚جƒsƒNƒZƒ‹ƒŒƒCƒAƒEƒg‚ًچج—p‚·‚é‚ة“–‚½‚ء‚ؤپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بRGB“ئ—§”Œُ•ûژ®ƒpƒlƒ‹‚و‚è‚à”’گFEL”Œُپ{ƒJƒ‰پ[ƒtƒBƒ‹ƒ^پ[(CF)•ûژ®ƒpƒlƒ‹‚ھ—L—ک‚ئ”»’fپB‚»‚±‚إپA••ژ~—pƒKƒ‰ƒXٹî”آ‚جƒ{ƒgƒ€–ت(ƒrƒ…پ[ƒڈپ[‘¤‚©‚猩‚ؤ)‚ة‚ـ‚¸RGB’…گF‘w‚ًƒtƒHƒgƒٹƒ\‚إŒ`گ¬پB‘±‚¢‚ؤپAƒgƒbƒv–ت‚ةƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒA‚ئ‚µ‚ؤCr/CrOƒuƒ‰ƒbƒNƒ}ƒgƒٹƒNƒX(BM)‚ًƒtƒHƒgƒٹƒ\‚إŒ`گ¬‚µ‚½پBˆê•ûپA”w–تٹî”آڈم‚ة‚حTFTپA‚»‚µ‚ؤƒ^ƒ“ƒfƒ€چ\‘¢‚ج”’گF—L‹@EL‘w‚ًŒ`گ¬پBچإŒم‚ةپA—¼–تٹî”آ‚ً“\‚èچ‡‚ي‚¹‚ؤƒpƒlƒ‹‰»‚µ‚½پB پ@ژژچى‚µ‚½‚ج‚ح5.2Œ^ƒpƒlƒ‹‚إپA•¨—“I‰ً‘œ“x‚ح1280پ~360‰و‘fپA•\ژ¦‰ً‘œ“x‚ح640پ~360‰و‘fپBƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒAپ`ƒsƒNƒZƒ‹ٹش‚ج‹——£‚ح500ƒتm‚إپAƒpƒlƒ‹‚جƒgپ[ƒ^ƒ‹Œْ‚ف‚ح1‡o‚ة‰ك‚¬‚ب‚¢پB‚±‚ê‚حپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚ب‰tڈ»ƒoƒٹƒA•ûژ®3D—L‹@ELD‚جŒْ‚³‚ھ2‡oˆبڈم‚إ‚ ‚é‚ج‚ة‘خ‚µ‘ه•‚ة”–Œ^Œy—ت‰»‚إ‚«‚邱‚ئ‚ًˆس–،‚·‚éپB پ@‚ئ‚±‚ë‚إپAƒpƒ‰ƒ‰ƒbƒNƒXƒoƒٹƒA•ûژ®‚ج3DƒfƒBƒXƒvƒŒƒC‚إ‚حƒoƒٹƒAƒpƒ^پ[ƒ“‚ج•‚ئ”z’uگ¸“x‚ھ‰وژ؟‚ة‘ه‚«‚ب‰e‹؟‚ً‹y‚ع‚·پBگ}3‚حƒoƒٹƒA•/ƒsƒbƒ`”ن‚جˆث‘¶گ«‚إپA‚ا‚ꂾ‚¯چ¶–ع—p‰و‘œ‚ئ‰E–ع—p‰و‘œ‚ھƒZƒpƒŒپ[ƒg‚إ‚«‚ؤ‚¢‚é‚©‚ًژ¦‚µ‚ؤ‚¢‚éپB‚±‚ج‚¤‚؟ڈم‚جگ}‚حƒoƒٹƒA•/ƒsƒbƒ`”نپپ0.58‚جڈêچ‡‚إپA‚»‚ꂼ‚ê‚ج‰و‘œ‚ح‚ظ‚عٹ®àّ‚ةƒZƒpƒŒپ[ƒg‚³‚ê‚ؤ‚¨‚èپAƒNƒچƒXƒgپ[ƒN‚à2.7پ“’ِ“x‚ئڈ¬‚³‚©‚ء‚½پB‚±‚±‚إ’چˆس‚·‚ׂ«‚حگ}’†‚جƒuƒ‰ƒbƒNƒ‰ƒCƒ“‚إپAƒ‚ƒAƒŒ‚ھ”نٹr“I‘½‚”گ¶‚µ‚½پB‚±‚ê‚ة‘خ‚µپA‰؛‚جگ}‚حƒoƒٹƒA•/ƒsƒbƒ`”نپپ0.5‚ة‚µ‚½ڈêچ‡‚إپAƒ‚ƒAƒŒ‚ھ‚ظ‚ئ‚ٌ‚ا”Fژ¯‚إ‚«‚ب‚©‚ء‚½پB پ@ژتگ^1‚ة3D•\ژ¦—ل‚ًژ¦‚·پBƒNƒچƒXƒgپ[ƒN‚ح5پ“ˆب‰؛‚إپA‹P“x‚ح250cd/m2پAگFچؤŒ»گ«‚حNTSC”ن109پ“پA”’گFگF“x‚حxپپ0.297پAyپپ0.309‚¾‚ء‚½پB

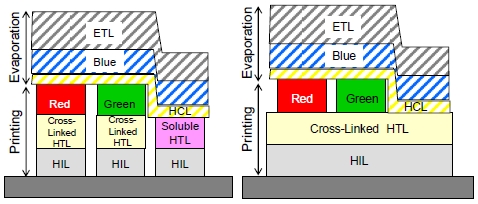

ƒvƒٹƒ“ƒ^ƒuƒ‹Œ^پ•ڈِ’…Œ^ƒnƒCƒuƒٹƒbƒhƒpƒlƒ‹‚جچ\‘¢‚ًƒVƒ“ƒvƒ‹‰» پ@ƒpƒlƒ‹‚جƒfƒUƒCƒ“‚إ‚حپAƒ\ƒjپ[‚ھƒvƒٹƒ“ƒ^ƒuƒ‹ƒŒƒCƒ„پ[‚ئڈِ’…ƒŒƒCƒ„پ[‚ً‘g‚فچ‡‚ي‚¹‚½ƒnƒCƒuƒٹƒbƒhƒpƒlƒ‹‚ًƒuƒ‰ƒbƒVƒ…ƒAƒbƒv‚µپAthe advanced hybrid device structure‚ئ–¼‚أ‚¯‚½ƒjƒ…پ[ƒXƒgƒ‰ƒNƒ`ƒƒپ[‚ً’ٌˆؤ‚µ‚½پB پ@“¯ژذ‚حˆب‘OپAگشگF—سŒُ”Œُ‘w‚ئ—خگF—سŒُ”Œُ‘w‚ًƒEƒFƒbƒgƒvƒچƒZƒX‚إچىگ»‚µپAگآگFŒuŒُ”Œُ‘w‚ً‹¤’تƒŒƒCƒ„پ[‚ئ‚µ‚ؤƒxƒ^ڈِ’…‚µ‚½ƒnƒCƒuƒٹƒbƒhƒfƒoƒCƒX‚ً”•\پB‚µ‚©‚µپAگ}4‚ج‚و‚¤‚ة‚»‚جƒŒƒCƒ„پ[چ\گ¬‚ح•،ژG‚إپAƒچپ[ƒRƒXƒg‚ب‘هŒ^ƒpƒlƒ‹‚ئ‚¢‚¤ƒtƒ@ƒCƒiƒ‹ƒSپ[ƒ‹‚ة‚حƒxƒXƒg‚ئ‚ح‚¢‚¦‚ب‚¢پB‚»‚±‚إپAچ،‰ٌ‚جƒjƒ…پ[ƒfƒoƒCƒX‚إ‚ح‚و‚背ƒCƒ„پ[چ\گ¬‚ًƒVƒ“ƒvƒ‹‚ة‚µ‚½پB‹ï‘ج“I‚ة‚حپA“h•zŒ^ƒzپ[ƒ‹’چ“ü‘w‚ئ“h•zŒ^ƒzپ[ƒ‹—A‘—‘w‚ًƒxƒ^‚إ“h•z‚µ‚ؤRGBٹe‘wŒü‚¯‚ة‹¤’ت‰»‚µپAگآگF”Œُ‘wگê—p‚ج“h•zŒ^ƒzپ[ƒ‹—A‘—‘w‚ًƒŒƒX‰»‚µ‚½پB

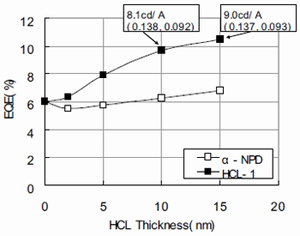

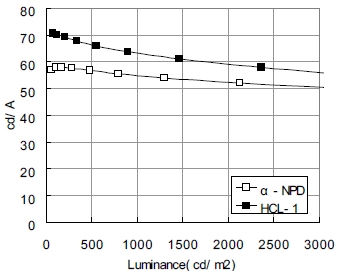

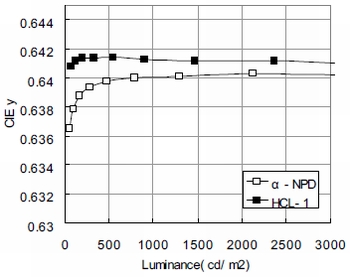

پ@گآگFŒuŒُ‘fژq‚جƒŒƒCƒ„پ[چ\گ¬‚ًŒ©’¼‚µ‚½‚ئ‚±‚ëپAڈِ’…Œ^”Œُ‘w‚ة‚ئ‚ء‚ؤ‚ح‰؛‘w‚ج‰ث‹´Œ^ƒzپ[ƒ‹—A‘—‘w‚حƒzپ[ƒ‹—A‘—گ«‚ھ•sڈ\•ھ‚إ‚ ‚邱‚ئ‚ھ‚ي‚©‚ء‚½پB‚آ‚ـ‚èپA“h•zŒ^ƒzپ[ƒ‹—A‘—‘w‚ئڈِ’…”Œُ‘w‚جٹE–ت‚ً‰ü‘P‚·‚é•K—v‚ھ‚ ‚éپB‚»‚±‚إپA‰ث‹´Œ^ƒzپ[ƒ‹—A‘—‘w‚جڈم•”‚ةڈِ’…Œ^‚جپuHCL-1پv‚ً—p‚¢‚邱‚ئ‚ة‚µ‚½پB‚»‚ج–ŒŒْ‚ً0پ`15nm‚ة‚µ‚ؤITOƒAƒmپ[ƒh/ƒzپ[ƒ‹’چ“ü‘w/‰ث‹´Œ^ƒzپ[ƒ‹—A‘—‘w/‹¤’تƒzپ[ƒ‹—A‘—‘w/گآگF”Œُ‘w/ƒzپ[ƒ‹‘jژ~‘w/“dژq—A‘—‘w/LiFƒoƒbƒtƒ@/AlƒJƒ\پ[ƒh‘fژq‚ًچىگ»‚µپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒ؟-NPD‘fژq‚ئ“ءگ«‚ً”نٹr‚µ‚½پB پ@گ}5‚ة“d—¬–§“x10mA/cm2ژ‚جٹO•”—تژqŒّ—¦‚ئƒzپ[ƒ‹—A‘—‘w–ŒŒْ‚جٹضŒW‚ًژ¦‚·پB‚ا‚؟‚ç‚جƒTƒ“ƒvƒ‹‚ئ‚àƒzپ[ƒ‹—A‘—‘w‚ج–ŒŒْ‚ھŒْ‚‚ب‚é‚ئŒّ—¦‚ھŒüڈم‚µپA–ŒŒْ15nm‚إŒّ—¦‚ھ9cd/A‚ئچإ‘ه‚ة‚ب‚èپAxپپ0.137پAyپپ0.093‚ئƒfƒBپ[ƒvƒuƒ‹پ[”Œُ‚ھ“¾‚ç‚ꂽپB

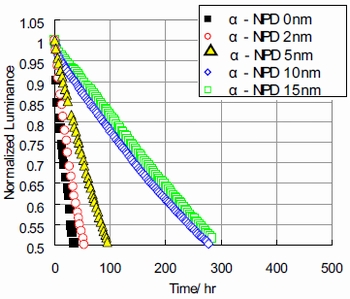

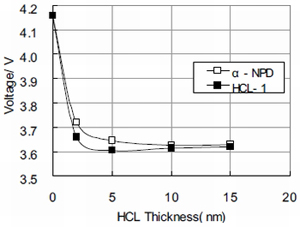

پ@گ}6‚ح“d—¬–§“x10mA/cm2ژ‚ج‹ى“®“dˆ³‚ئƒzپ[ƒ‹—A‘—‘w–ŒŒْ‚جٹضŒW‚إپAƒzپ[ƒ‹—A‘—‘w‚ج–ŒŒْ‚ھŒْ‚‚ب‚é‚ئ‹ى“®“dˆ³‚à’ل‰؛‚µ‚½پB‚ـ‚½پA“ٌ‚آ‚جƒTƒ“ƒvƒ‹‚ً”نٹr‚·‚é‚ئپAHCL-1‘fژq‚ج•û‚ھ‚ي‚¸‚©‚¾‚ھƒ؟-NPD‘fژq‚و‚è‚à“dˆ³‚ھ’ل‰؛‚µ‚½پB‚±‚ê‚ç‚جŒ‹‰ت‚حپA‰ث‹´Œ^ƒzپ[ƒ‹—A‘—‘w‚جٹE–ت‚ھڈِ’…Œ^ƒzپ[ƒ‹—A‘—چق—؟‚جڈِ’…‚ة‚و‚ء‚ؤ‰ü‘P‚µ‚½‚½‚ك‚ئچl‚¦‚ç‚ê‚éپB پ@گ}7پA8‚حƒzپ[ƒ‹—A‘—‘w‚ج–ŒŒْ‚ئƒ‰ƒCƒtƒ^ƒCƒ€‚جٹضŒW‚إپA‚ا‚؟‚ç‚à–ŒŒْ‚ً10nmˆبڈم‚ة‚·‚é‚ئƒ‰ƒCƒtƒ^ƒCƒ€‚ھŒ€“I‚ةŒüڈمپB‚ئ‚‚ةپAHCL-1‘fژq‚جƒGƒ“ƒnƒ“ƒXƒپƒ“ƒgŒّ‰ت‚ھŒ°’ک‚¾‚ء‚½پB‚±‚ê‚حپAHCL-1‘fژq‚ج•û‚ھƒzپ[ƒ‹—A‘—“ءگ«ŒüڈمŒّ‰ت‚ھچ‚‚¢‚½‚ك‚ئچl‚¦‚ç‚ê‚éپB پ@ˆê•ûپA—خگF—سŒُ‘fژq‚ة‚¨‚¯‚éHTL-1‚جŒّ‰تپA‚آ‚ـ‚èژOڈdچ€—م‹Nڈَ‘ش‚ًŒںڈط‚·‚邽‚كپAڈِ’…Œ^ƒzپ[ƒ‹—A‘—‘w‚ج–ŒŒْ‚ً10nm‚ةŒإ’肵پAITOƒAƒmپ[ƒh/ƒzپ[ƒ‹’چ“ü‘w/‰ث‹´Œ^ƒzپ[ƒ‹—A‘—‘w/—خگF”Œُ‘w/ڈِ’…Œ^ƒzپ[ƒ‹—A‘—‘w/ƒzپ[ƒ‹‘jژ~‘w/“dژq—A‘—‘w/LiFƒoƒbƒtƒ@‘w/AlƒJƒ\پ[ƒh‘fژq‚ًچىگ»پBƒ؟-NPD‘fژq‚ئHTL-1‘fژq‚ج“ءگ«‚ً”نٹr‚µ‚½پBگ}9‚ح‘fژq‚ج“d—¬Œّ—¦‚إپAHCL-1‘fژq‚حژہ—p‹P“xƒŒƒ“ƒW‘Sˆو‚ة‚ي‚½‚ء‚ؤچ‚‚¢Œّ—¦‚ھ“¾‚ç‚ꂽپBگ}10‚حCIEگF“x‚ج•]‰؟Œ‹‰ت‚إپAHCL-1‘fژq‚حژہ—p‹P“xƒŒƒ“ƒW‘Sˆو‚ة‚ي‚½‚ء‚ؤ—اچD‚بگF“x‚ھˆغژ‚إ‚«‚ؤ‚¢‚é‚ج‚ھ‚ي‚©‚éپB‚±‚ê‚ة‘خ‚µپAƒ؟-NPD‘fژq‚ح’ل‹P“x—جˆو‚إگآگF”Œُ‚ھٹدژ@‚³‚ê‚邱‚ئ‚©‚çگF“x•د‰»‚ھ‘ه‚«‚©‚ء‚½پB

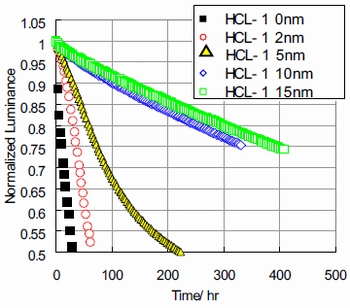

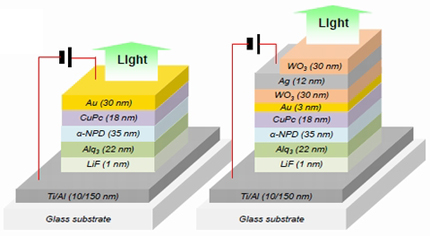

پ@‚ئ‚±‚ë‚إپA—سŒُ‘fژq‚جƒzپ[ƒ‹‘jژ~‘w‚ة‚حچL‚BCP‚ھ—p‚¢‚ç‚ê‚é‚ھپAچ،‰ٌ‚جƒnƒCƒuƒٹƒbƒhƒfƒoƒCƒX‚إ‚حƒzپ[ƒ‹‘jژ~Œّ‰ت‚ھ•sڈ\•ھ‚إ‚ ‚邽‚كپAڈِ’…ƒzپ[ƒ‹—A‘—‘w‚ًژOڈdچ€—م‹NژqƒuƒچƒbƒLƒ“ƒOƒŒƒCƒ„پ[‚ئ‚µ‚ؤ‹@”\‚³‚¹‚½پB‚¢‚¤‚ـ‚إ‚à‚ب‚پA—سŒُ‘fژq‚ة‚ئ‚ء‚ؤT1(ژOڈdچ€—م‹Nڈَ‘ش)ƒGƒlƒ‹ƒMپ[ƒŒƒxƒ‹‚ح‚«‚ي‚ك‚ؤڈd—v‚إ‚ ‚èپA‚»‚ج’l‚حHCL-1پ„—خگF—سŒُ”Œُچق—؟پ„ƒ؟-NPD‚¾‚ء‚½پB‚±‚ج‚½‚كپAHCL-1‚ً—p‚¢‚é‚ئپA—خگF”Œُ‚جژOڈdچ€—م‹Nژq‚ً•آ‚¶چ‚ك‚ؤگآگF”Œُ‚ج”گ¶‚ً—}گ§‚·‚邱‚ئ‚ھ‚إ‚«‚éپB‚±‚ê‚ة‘خ‚µپAƒ؟-NPD‚ح—خگF—سŒُ”Œُچق—؟‚و‚è‚àT1‚ھڈ¬‚³‚¢‚½‚كپA—خگF”Œُ’†‚ةگآگF”Œُ‚ھٹدژ@‚³‚ê‚éپB‚±‚¤‚µ‚½Œ»ڈغ‚حگشگF”Œُ‘fژq‚ة‚à‹¤’ت‚·‚éپB‚·‚ب‚ي‚؟پAT1‚ھچ‚‚¢HCL-1‚جچج—p‚ة‚و‚ء‚ؤRGB”Œُ‚ئ‚à“ءگ«‚ھ‰ü‘P‚إ‚«‚é‚ي‚¯‚إ‚ ‚éپB پ@ژQچl‚ئ‚µ‚ؤپA•\1‚ةHCL-1‚ج–ŒŒْ‚ً10nm‚ة‚µ‚½چغ‚جRGB”Œُ“ءگ«‚ًژ¦‚·پB WO3/Ag/WO3ƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚ً‹tچ\‘¢ƒgƒbƒvƒGƒ~ƒbƒVƒ‡ƒ“ƒpƒlƒ‹‚جƒAƒmپ[ƒh‚ة پ@‹tچ\‘¢ƒgƒbƒvƒGƒ~ƒbƒVƒ‡ƒ“ƒpƒlƒ‹‚جƒLپ[ƒ|ƒCƒ“ƒg‚ئ‚à‚¢‚¦‚铧–¾ƒgƒbƒvƒAƒmپ[ƒh‚ةٹض‚µ‚ؤ‚حپAPohang University of Science and Engineering(ٹطچ‘)‚ھWO3/Ag/WO3(WAW)ƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚ً’ٌˆؤ‚µ‚½پB پ@WAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚حƒ{ƒgƒ€ƒGƒ~ƒbƒVƒ‡ƒ“ƒpƒlƒ‹‚جƒ{ƒgƒ€ƒAƒmپ[ƒh‚âƒgƒbƒvƒGƒ~ƒbƒVƒ‡ƒ“ƒpƒlƒ‹‚جƒgƒbƒvƒJƒ\پ[ƒh‚ة‚à“K—p‚إ‚«‚邱‚ئ‚ھ’m‚ç‚ê‚ؤ‚¢‚é‚ھپA‹tچ\‘¢ƒgƒbƒvƒGƒ~ƒbƒVƒ‡ƒ“ƒpƒlƒ‹‚جƒgƒbƒvƒAƒmپ[ƒh‚إ‚حƒzپ[ƒ‹’چ“ü“ءگ«‚ھڈ\•ھ‚ئ‚ح‚¢‚¦‚ب‚¢پB‚±‚ج‚½‚كپA‰؛•”‚ة‹ة”––ŒAu‚ًگف‚¯‚½پB‚ـ‚½پAWAW‚ًƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒXƒpƒbƒ^ƒٹƒ“ƒO–@‚إگ¬–Œ‚·‚é‚ئ‰؛‘w‚ج—L‹@‘w‚ض‚جƒ_ƒپپ[ƒW‚ھŒœ”O‚³‚ê‚邽‚كپA’ïچR‰ء”Mڈِ’…–@‚ة‚و‚ء‚ؤ‚±‚ê‚ç‚ًکA‘±گ¬–Œ‚µ‚½پB پ@ƒpƒlƒ‹‚جچ\‘¢‚حگ}11‚ج‰Eگ}‚ج’ت‚è‚إپAگôڈٍ‚µ‚½ٹî”آڈم‚ة‚ـ‚¸Ti/AlƒJƒ\پ[ƒh‚ًڈِ’…پB‘±‚¢‚ؤپALiFƒoƒbƒtƒ@‘wپAAlq3“dژq—A‘—Œ“”Œُ‘wپAƒ؟-NPDƒzپ[ƒ‹—A‘—‘wپACuPcƒzپ[ƒ‹’چ“ü‘w‚ًکA‘±ڈِ’…‚µ‚½پB‘±‚¢‚ؤپA‘O‹L‚ج‚و‚¤‚ةƒzپ[ƒ‹’چ“ü“ءگ«‚ً‰ü‘P‚·‚邽‚كپAAu–Œ‚ً–ŒŒْ3nm‚إڈِ’…پB‚»‚µ‚ؤپAWO3(30nm)/Ag/WO3(30nm)ƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[ƒAƒmپ[ƒh‚ًڈِ’…‚µ‚½پB‚±‚±‚إAg‚ج–ŒŒْ‚ً10پ`25nm‚ئ•د‚¦‚ؤ“ءگ«‚ھ‚ا‚¤•د‰»‚·‚é‚©’²‚ׂ½پB

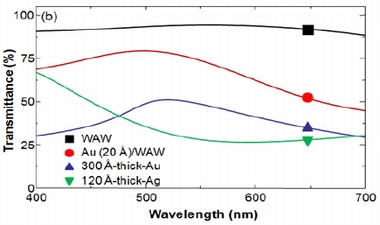

پ@گ}12‚ةWAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚ج‰آژ‹Œُ“§‰ك—¦(@520nm)‚ًژ¦‚·پB‰آژ‹Œُ‘Sˆو‚ة‚ي‚½‚ء‚ؤ90پ“‘OŒم‚ئچ‚‚¢“§‰ك—¦‚ھ“¾‚ç‚êپA‚ئ‚‚ةAg–ŒŒْ12nm‚إ93.7پ“‚ئچإچ‚‚ج’l‚ھ“¾‚ç‚ꂽپB“ء’è‚جAg–ŒŒْ‚إ“§‰ك—¦‚ھŒüڈم‚µ‚½‚ج‚حپAWAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚جŒُٹw“ءگ«‚ھAg‚ج•\–تƒvƒ‰ƒYƒ‚ƒ“‹¤–آŒّ‰ت‚ة‚و‚ء‚ؤگ§Œن‚³‚ꂽ‚½‚ك‚ئچl‚¦‚ç‚ê‚éپB‚ب‚¨پA‚±‚جƒPپ[ƒX‚ة‚¨‚¯‚éƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚جƒVپ[ƒg’ïچR’l‚ح10ƒ¶/پ ˆب‰؛‚¾‚ء‚½پBˆê•ûپAAg–ŒŒْ‚ً8nm‚©‚ç25nm‚ة‘‰ء‚³‚¹‚é‚ئپAƒVپ[ƒg’ïچR’l‚ح9.85ƒ¶/پ ‚©‚ç7.22ƒ¶/پ ‚ض’ل‰؛‚µ‚½پB‚±‚ê‚ç‚جŒ‹‰ت‚حAg–ŒŒْ‚ة‚و‚ء‚ؤ“±“dگ«‚ھŒˆ‚ـ‚邱‚ئ‚ًˆس–،‚·‚éپBگ}13‚حWAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[پAAuپAAg‚ج“§‰ك—¦‚إپA–ŒŒْ30nm‚جAu–Œ‚ح50.8پ“پA–ŒŒْ12nm‚جAg–Œ‚ح31.5پ“(‚¢‚¸‚ê‚à@520nm)‚¾‚ء‚½پB“ء•M‚³‚ê‚é‚ج‚حپAWAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[‚ة‚¨‚¯‚éAg–ŒŒْ‚ھ”–‚¢‚ئپA‚»‚ج“§‰ك—¦‚ح93.7پ“‚ئAg’P–Œ‚و‚è‚àچ‚‚¢“§‰ك—¦‚ًژ¦‚µ‚½‚±‚ئ‚إ‚ ‚éپB

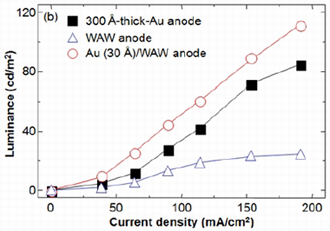

پ@‚µ‚©‚µپAƒٹƒtƒ@ƒŒƒ“ƒX‚إ‚ ‚éAuƒAƒmپ[ƒh(–ŒŒْ30nm)ƒpƒlƒ‹‚ئWAWƒpƒlƒ‹‚ج‹ى“®“dˆ³‚ً”نٹr‚·‚é‚ئپA‘Oژز‚ح“d—¬–§“x10mA/cm2‚ة‚¨‚¯‚é‹ى“®“dˆ³‚ھ10.2V‚¾‚ء‚½‚ج‚ة‘خ‚µپAŒمژز‚ح13.4V‚ئڈمڈ¸‚µ‚½پB‚»‚±‚إپA‘O‹L‚ج‚و‚¤‚ةCuPc–Œ‚ئWAWƒ}ƒ‹ƒ`ƒŒƒCƒ„پ[ٹش‚ة–ŒŒْ3nm‚جAu–Œ‚ًƒCƒ“ƒ^پ[ƒŒƒCƒ„پ[‚ئ‚µ‚ؤ‘}“ü‚µ‚½‚ئ‚±‚ëپA‹ى“®“dˆ³‚ح10.3V‚ئŒ€“I‚ة’ل‰؛‚µ‚½پB‚±‚ê‚حپA“à•”—تژqŒّ—¦Œّ‰ت‚ة‚و‚ء‚ؤƒzپ[ƒ‹’چ“ü“ءگ«‚ھ‰ü‘P‚³‚ꂽ‚±‚ئ‚ًژ¦‚·پBژہچغپAAu‚جژdژ–ٹضگ”‚ح4.95eV‚ئŒ©گد‚à‚ç‚êپAƒCƒIƒ“‰»ƒ|ƒeƒ“ƒVƒƒƒ‹‚ھ4.8پ`5.2eV‚إ‚ ‚éCuPc‚ئ‚جƒLƒƒƒٹƒAڈل•ا‚ھ’ل‚¢‚±‚ئ‚ھٹm”F‚إ‚«‚½پB‚±‚ê‚ç‚جŒ‹‰تپAAuƒAƒmپ[ƒhƒpƒlƒ‹‚ة”ن‚×گVچ\‘¢ƒAƒmپ[ƒhƒpƒlƒ‹‚ح‹P“x‚ھ32پ“Œüڈم‚·‚éپB ƒpƒ‹ƒX“dˆ³ˆَ‰ء‚ة‚و‚éƒWƒ…پ[ƒ‹”M‚إŒ³ٹî”آ‚©‚çƒvƒ‰ƒXƒ`ƒbƒNگ»—L‹@ELD‚ًƒٹƒٹپ[ƒX

پ@ƒtƒŒƒLƒVƒuƒ‹—L‹@ELD‚إ‚حپASamsung Electronics‚ئEnSilTech‚ھƒKƒ‰ƒXٹî”آڈم‚ةچىگ»‚µ‚½ƒAƒNƒeƒBƒu‹ى“®—L‹@ELD‚ًJILO(Joule heating induced lift-off)‚ئ–¼‚أ‚¯‚½•û–@‚ة‚و‚ء‚ؤƒٹƒٹپ[ƒX‚µ‚½ƒvƒ‰ƒXƒ`ƒbƒNگ»—L‹@ELD‚ً”•\‚µ‚½پB پ@JILOƒvƒچƒZƒX‚إ‚حپAƒIƒٹƒWƒiƒ‹ٹî”آ‚إ‚ ‚éƒKƒ‰ƒXٹî”آ‚ئƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€ٹش‚ة“±“d‘w‚ًگف‚¯‚éپB“±“d‘w‚ج–ŒŒْ‚حJILOƒvƒچƒZƒX‚جƒWƒ…پ[ƒ‹”M‚ة‘د‚¦‚ç‚ê‚é‚و‚¤چإ“K‰»‚·‚éپBƒtƒ@ƒCƒiƒ‹ƒTƒuƒXƒgƒŒپ[ƒg‚ئ‚ب‚éƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€‚ح—L‹@گâ‰ڈچق—؟‚ً–ŒŒْ10ƒتm‚إ“h•z‚µ‚½ŒمپA350پژ‚إچd‰»‚³‚¹‚ؤƒtƒBƒ‹ƒ€‰»‚·‚éپB‚±‚جŒمپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒvƒچƒZƒX‚إ’ل‰·Poly-Si TFTپA‘±‚¢‚ؤ—L‹@EL‚ًŒ`گ¬‚µ‚½ŒمپA”––Œ••ژ~‚·‚éپB‚»‚µ‚ؤپAچإŒم‚ةJILOƒvƒچƒZƒX‚ة‚و‚ء‚ؤŒ³ƒKƒ‰ƒXٹî”آ‚©‚çƒvƒ‰ƒXƒ`ƒbƒNگ»ƒpƒlƒ‹‚ًƒٹƒٹپ[ƒX‚·‚éپB پ@‚»‚جJILOƒvƒچƒZƒX‚¾‚ھپAƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€‚ج’¼‰؛‚ة‘¶چف‚·‚铱“d‘w‚©‚ç”گ¶‚·‚éƒWƒ…پ[ƒ‹”M‚ً—p‚¢‚éپB“±“d‘w‚ةƒتsƒIپ[ƒ_پ[‚إƒpƒ‹ƒX“dˆ³‚ًڈuٹش“I‚ةˆَ‰ء‚·‚éژd‘g‚ف‚إپA‚±‚جچغ‚ة”گ¶‚·‚éƒWƒ…پ[ƒ‹”M‚حƒ†ƒjƒtƒHƒ~ƒeƒB‚و‚ƒvƒ‰ƒXƒ`ƒbƒNٹî”آ‘S–ت‚ض“`“±‚·‚éپB‚±‚ج‚½‚كپA•¨—“Iƒ_ƒپپ[ƒWƒŒƒX‚إŒ³ٹî”آ‚©‚çƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€گ»ƒpƒlƒ‹‚ھƒٹƒٹپ[ƒX‚إ‚«‚éپB پ@ƒ_ƒپپ[ƒWƒtƒٹپ[ƒٹƒٹپ[ƒX‚ًژہŒ»‚·‚邽‚كپA“±“d‘w‚ض‚جƒpƒ‹ƒX“dˆ³‚ًˆَ‰ء‚µ‚½چغ‚ج”M“`“±‚ًƒVƒ~ƒ…ƒŒپ[ƒg‚µ‚½‚ئ‚±‚ëپAƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€/“±“d‘w/ƒKƒ‰ƒXٹî”آ3‘w‚ة”گ¶‚·‚éƒWƒ…پ[ƒ‹”M‚حƒ}ƒbƒNƒX600پژ‚ة’B‚·‚邱‚ئ‚ھ‚ي‚©‚ء‚½پB‚±‚جچغپAƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€‚ئ“±“d‘w‚جٹE–ت‚ح450پژˆبڈم‚ة‚ب‚éپB‚آ‚ـ‚èپAƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€‚ج—Z“_‚ً’´‚¦‚éپB‚±‚جŒ‹‰تپAŒ³ƒKƒ‰ƒXٹî”آ‚©‚ç—eˆص‚ةƒٹƒٹپ[ƒX‚إ‚«‚é‚ي‚¯‚إ‚ ‚éپB‚±‚جچغپAƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€“à•”‚ضگZ“§‚·‚é”Mگ[‚³‚ح1ƒتmˆب‰؛‚ة‰ك‚¬‚ب‚¢پB‚±‚ج‚½‚كپAچ‚‰·ƒvƒچƒZƒX‚إ‚ ‚è‚ب‚ھ‚ç”Mƒ_ƒپپ[ƒWƒŒƒX‚إƒٹƒٹپ[ƒX‚·‚邱‚ئ‚ھ‚إ‚«‚éپBژتگ^2‚حƒٹƒٹپ[ƒX‚ج—lژq‚إپAژè‚إ—eˆص‚ةƒٹƒٹپ[ƒX‚·‚邱‚ئ‚ھ‚إ‚«‚éپB

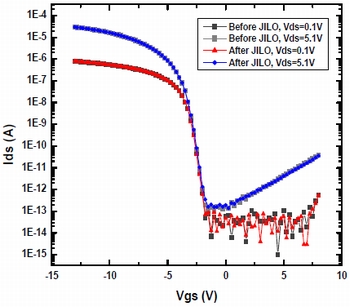

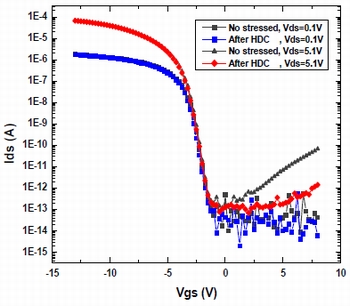

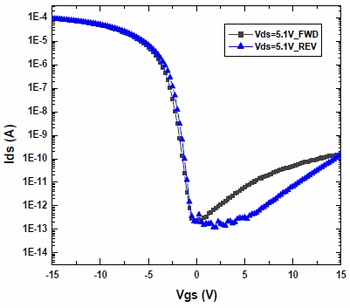

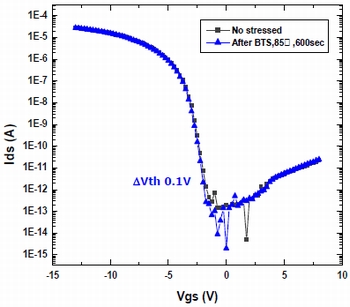

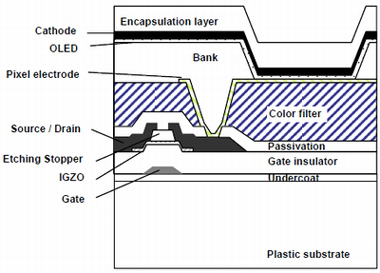

پ@گ}15‚ةJILOƒvƒچƒZƒX‘OŒم‚جTFT“ءگ«‚ًژ¦‚·پBJILOƒvƒچƒZƒX‘O‚ج“ءگ«‚حƒLƒƒƒٹƒAƒ‚ƒrƒٹƒeƒB‚ھ90cm2/V¥sپAVth‚ھپ|2.9VپAON/OFF“d—¬ƒŒƒVƒI‚ھ108پAƒTƒuƒXƒŒƒbƒVƒ‡ƒ‹ƒhƒXƒچپ[ƒv‚ھ0.32V/decade‚¾‚ء‚½پB‚±‚ê‚ة‘خ‚µپAJILOƒvƒچƒZƒXŒم‚à“ءگ«‚ح‚ظ‚ئ‚ٌ‚ا•د“®‚µ‚ب‚©‚ء‚½پB‚¢‚¤‚ـ‚إ‚à‚ب‚پA‚±‚ê‚حJILOƒvƒچƒZƒX‚ھTFT‚ة‚ظ‚ئ‚ٌ‚اƒ_ƒپپ[ƒW‚ً—^‚¦‚ب‚¢‚±‚ئ‚ًˆس–،‚·‚éپB پ@گ}16‚ح85پژ‚إƒoƒCƒAƒXƒXƒgƒŒƒX15V‚ً600•bˆَ‰ء‚µ‚½چغ‚جƒgƒ‰ƒ“ƒXƒtƒ@پ[“ءگ«‚إپAVthƒVƒtƒg‚ح0.1V‚ة‰ك‚¬‚ب‚©‚ء‚½پB‚±‚ê‚حپAƒKƒ‰ƒXٹî”آڈم‚ةچىگ»‚µ‚½’ل‰·Poly-Si TFT‚ئ‚ظ‚ع“¯‚¶‚إ‚ ‚éپB‚³‚ç‚ةپAگ}17‚ج‚و‚¤‚ةVgsپپپ|15VپAVdsپپپ|20V‚ً60•bˆَ‰ء‚µ‚½ƒnƒCƒhƒŒƒCƒ““d—¬ƒeƒXƒg‚إ‚à“ءگ«‚ح‚ظ‚ئ‚ٌ‚ا•د‰»‚µ‚ب‚©‚ء‚½پBگ}18‚حƒqƒXƒeƒٹƒVƒX“ءگ«‚ً•]‰؟‚µ‚½‚à‚ج‚إپAJILOƒvƒچƒZƒXŒم‚جVthƒVƒtƒg‚ح0.2V‚ئƒKƒ‰ƒXگ»’ل‰·Poly-Si TFT‚ئ‚ظ‚ع“¯‚¶‚¾‚ء‚½پB پ@‚±‚ê‚ç‚جŒ‹‰ت‚©‚çپAJILOƒvƒچƒZƒX‚حڈ]—ˆ‚ج‚¨‚à‚بƒٹƒٹپ[ƒX•û–@‚ئ‚µ‚ؤ’m‚ç‚ê‚郌پ[ƒUپ[”چ—£–@‚ة”ن‚׈ہ‰؟‚إ‚©‚آچ‚‘¬‚بƒvƒچƒZƒX‚إ‚ ‚èپA—تژY‚ةچإ“K‚ئŒ‹ک_‚أ‚¯‚½پB ƒvƒ‰ƒXƒ`ƒbƒNٹî”آڈم‚ةIGZO-TFT‚ًƒ_ƒCƒŒƒNƒgŒ`گ¬ پ@ˆê•ûپA“Œژإ‚حƒAƒ‚ƒ‹ƒtƒ@ƒXIGZOژ_‰»•¨TFT‚إƒhƒ‰ƒCƒu‚·‚é3Œ^ƒtƒŒƒLƒVƒuƒ‹—L‹@ELD‚ً”•\‚µ‚½پB‚±‚؟‚ç‚حƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€ڈم‚ة’¼گعTFT‚ئ—L‹@EL‚ًŒ`گ¬‚·‚éƒAƒvƒچپ[ƒ`‚إپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒKƒ‰ƒXگ»ƒpƒlƒ‹‚ة•C“G‚·‚é“ءگ«‚ھ“¾‚ç‚ꂽپB پ@ƒTƒuƒXƒgƒŒپ[ƒg‚ة‚ح“§–¾‚بƒvƒ‰ƒXƒ`ƒbƒNƒtƒBƒ‹ƒ€‚ًژg—pپB‚ـ‚¸پAگ…‚ب‚ا‚ج•sڈƒ•¨ƒKƒX‚ًƒuƒچƒbƒN‚·‚邽‚كپAٹî”آ‰·“x200پژ‚إƒoƒbƒtƒ@چق—؟‚ًگ¬–Œ‚µ‚½پB‘±‚¢‚ؤپAƒGƒbƒ`ƒ“ƒOƒXƒgƒbƒpپ[•t‚«ƒ{ƒgƒ€ƒQپ[ƒgچ\‘¢‚جIGZO-TFT‚ًچىگ»‚µ‚½پB‹ï‘ج“I‚ة‚حپA‚ـ‚¸ƒQپ[ƒgƒپƒ^ƒ‹‚ًƒXƒpƒbƒ^ƒٹƒ“ƒOگ¬–Œ‚µ‚ؤƒtƒHƒgƒٹƒ\پ{ƒhƒ‰ƒCƒGƒbƒ`ƒ“ƒO‚إƒpƒ^پ[ƒjƒ“ƒOپBƒQپ[ƒgگâ‰ڈ–Œ‚ًگ¬–Œ‚µ‚½ŒمپAO2ƒKƒXƒpپ[ƒW•µˆح‹C‚إƒAƒ‚ƒ‹ƒtƒ@ƒXIGZO–Œ‚ًƒXƒpƒbƒ^ƒٹƒ“ƒOگ¬–Œ‚µپAƒtƒHƒgƒٹƒ\‚إƒpƒ^پ[ƒjƒ“ƒO‚µ‚½پB‘±‚¢‚ؤپAIGZO–Œڈم‚ةƒGƒbƒ`ƒ“ƒOƒXƒgƒbƒpپ[‚ًŒ`گ¬پBƒRƒ“ƒ^ƒNƒgƒzپ[ƒ‹Œ`گ¬ŒمپAƒ\پ[ƒX/ƒhƒŒƒCƒ““d‹ة‚ئƒpƒbƒVƒxپ[ƒVƒ‡ƒ“‚ًŒ`گ¬‚µ‚½پB‚ـ‚½پAƒQپ[ƒgƒhƒ‰ƒCƒo‰ٌکH120Œآ‚ًٹî”آڈم‚ةƒrƒ‹ƒgƒCƒ“‚µ‚½پB‚ب‚¨پATFTچ\گ¬‚حƒVƒ“ƒvƒ‹‚ب2TFT-1C‚إ‚ ‚éپB پ@‘¼•ûپA—L‹@ELD‚حگ}19‚ج‚و‚¤‚ةƒ{ƒgƒ€ƒGƒ~ƒbƒVƒ‡ƒ“چ\‘¢‚ج”’گFELپ{ƒJƒ‰پ[ƒtƒBƒ‹ƒ^پ[ƒIƒ“ƒAƒŒƒC(COA)•ûژ®‚ًچج—p‚µ‚½پB‚ـ‚¸پAƒJƒ‰پ[ƒŒƒWƒXƒg‚ً“h•z‚µƒtƒHƒgƒٹƒ\‚إƒpƒ^پ[ƒjƒ“ƒO‚µ‚ؤCOA‚ًŒ`گ¬پB‘±‚¢‚ؤپAƒAƒmپ[ƒh‰و‘f“d‹ة‚ًگ¬–ŒپEƒpƒ^پ[ƒjƒ“ƒOپBژں‚ةپAƒTƒuƒsƒNƒZƒ‹‚ًژdگط‚éƒoƒ“ƒN‚ًŒ`گ¬‚µ‚½پB‚±‚جŒمپAƒzپ[ƒ‹—A‘—‘wپA”Œُ‘wپA“dژq—A‘—‘wپAƒJƒ\پ[ƒh‚ًکA‘±ڈِ’…‚µپAچإŒم‚ة••ژ~‘w‚إ••ژ~‚µ‚½پB

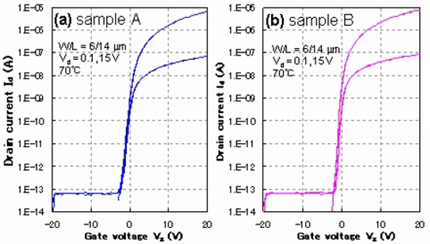

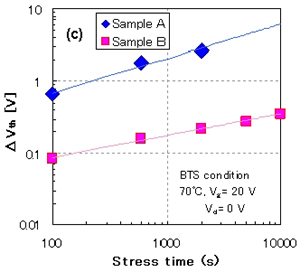

پ@IGZO-TFT“ءگ«‚ً•]‰؟‚µ‚½‚ئ‚±‚ëپA–Oکa—جˆو‚ة‚¨‚¯‚éƒLƒƒƒٹƒAƒ‚ƒrƒٹƒeƒB‚ح11.6cm2/V¥sپAVth‚ح1.6VپAƒXƒŒƒbƒVƒ‡ƒ‹ƒhƒXƒچپ[ƒv‚ح0.25V/dec‚ئ—اچD‚¾‚ء‚½پB‚½‚¾پAژلٹ±‚جƒqƒXƒeƒٹƒVƒX‚ھ‚ف‚ç‚ꂽپB پ@ƒ|ƒXƒgƒAƒjپ[ƒ‹ڈًŒڈ‚جˆظ‚ب‚éƒTƒ“ƒvƒ‹A‚ئƒTƒ“ƒvƒ‹B‚ًچىگ»‚µپA70پژژ‚جTFTڈ‰ٹْ“ءگ«‚ئBTSƒeƒXƒg’†‚جVth‚ً”نٹr‚µ‚½‚ئ‚±‚ëپAگ}20-(a)پA(b)‚ج‚و‚¤‚ة‚ا‚؟‚ç‚جƒTƒ“ƒvƒ‹‚ئ‚àڈ‰ٹْ“ءگ«‚ح“¯‚¶‚¾‚ء‚½پB‘¼•ûپAƒQپ[ƒg“dˆ³پ}20VپAƒhƒŒƒCƒ““dˆ³0V‚إچs‚ء‚½BTSƒeƒXƒgŒم‚جVthƒVƒtƒg‚ح‘ه‚«‚ˆظ‚ب‚èپAƒTƒ“ƒvƒ‹B‚جVthƒVƒtƒg‚ح2000•bŒم‚إ0.22VپA1–œ•bŒم‚إ0.35V‚¾‚ء‚½پB‚±‚ê‚حƒTƒ“ƒvƒ‹A‚ج1/10ˆب‰؛‚ة“–‚½‚èپAƒKƒ‰ƒXٹî”آڈم‚ةƒvƒچƒZƒX‰·“x300پژˆبڈم‚إچىگ»‚µ‚½IGZO-TFT‚ج’l‚ة‹ك‚¢پB‚آ‚ـ‚èپAƒAƒjپ[ƒ‹ڈًŒڈ‚ًچإ“K‰»‚·‚ê‚خپAƒvƒچƒZƒX‰·“x200پژ‚إ‚àƒKƒ‰ƒXگ»TFT‚ئ“¯‚¶“ءگ«‚ھ“¾‚ç‚ê‚é‚ي‚¯‚إ‚ ‚éپB

SGS Poly-Si‚ح‘و6گ¢‘مٹî”آ‚إ‚àƒOƒŒƒCƒ“ƒTƒCƒY‚ھ—eˆص‚ةگ§Œن‰آ”\ پ@—L‹@ELD—pTFT‚إ‚حپAٹطچ‘‚جگ^‹َ‘•’uƒپپ[ƒJپ[‚إ‚ ‚éIRUJA‚ھƒGƒLƒVƒ}ƒŒپ[ƒUپ[ƒAƒjپ[ƒ‹–@‚ة‘م‚ي‚éPoly-SiŒ‹ڈ»‰»•û–@‚ئ‚µ‚ؤSuper Grain Silicon(SGS)ƒeƒNƒmƒچƒWپ[‚ًڈذ‰îپB1500پ~1850mm‚ج‘و6گ¢‘مƒ}ƒUپ[ƒKƒ‰ƒXڈم‚ةSGS Poly-Si‚ًچىگ»‚µپAƒeƒŒƒr—p‚ً‚ح‚¶‚ك‚ئ‚·‚é‘هŒ^—L‹@ELD‚ة‚à—eˆص‚ة‘خ‰‰آ”\‚ب‚±‚ئ‚ًژ¦‚µ‚½پB پ@ژü’m‚ج‚و‚¤‚ةپASGS‚ح‚ـ‚¸a-SiƒvƒٹƒJپ[ƒT–Œ‚ة’ل–§“x‚إ—±ژqڈَ‚جNi‚ً“üژثپB‚»‚جŒم‚ج”Mڈˆ—‚ة‚و‚ء‚ؤSi‚جƒVپ[ƒh‚ئ‚µ‚ؤ‹@”\‚µ‚ؤSiƒOƒŒƒCƒ“‚ًŒ‹ڈ»‰»‚·‚éژd‘g‚فپB‚±‚±‚إڈd—v‚ب‚ج‚حNi—±ژq‚جگ¬–ŒƒvƒچƒZƒX‚إپA‚»‚ج–§“x‚ئƒOƒŒƒCƒ“ƒTƒCƒY‚ة‚و‚ء‚ؤƒٹپ[ƒN“d—¬‚ب‚ا‚جTFT“ءگ«‚ھŒˆ‚ـ‚éپB پ@‚»‚جNiگ¬–Œ–@‚حپAƒXƒpƒbƒ^ƒٹƒ“ƒOگ¬–Œ’†‚ةٹî”آ‚ًˆع“®‚³‚¹‚é•û–@‚ھ’m‚ç‚ê‚éپB‚µ‚©‚µپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒXƒpƒbƒ^ƒٹƒ“ƒO‘•’u‚إ‚ح20پ`40•b‚إگ”ƒتm‚ة‚ـ‚إ–Œ‚ھ‘حگد‚µ‚ؤ‚µ‚ـ‚¤پB‚»‚±‚إپA“¯ژذ‚ح‹ة’[‚ة’ل‚¢گ¬–ŒƒŒپ[ƒg‚إNiŒ´ژq‚ً“üژث‚³‚¹‚ؤƒTƒuپً–ŒŒْ‚ة‚à‘خ‰‰آ”\‚بƒXƒpƒbƒ^ƒٹƒ“ƒO‘•’u‚ًٹJ”پB‘و6گ¢‘مٹî”آ‘خ‰‘•’u‚ةƒXƒPپ[ƒ‹ƒAƒbƒv‚µ‚½پB

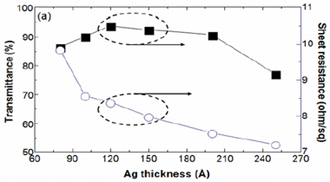

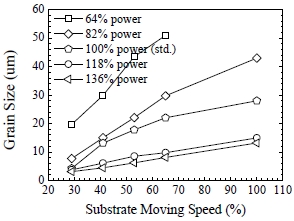

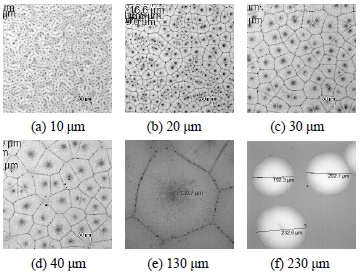

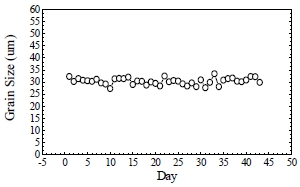

پ@‚±‚جNi–Œگê—pƒXƒpƒbƒ^ƒٹƒ“ƒO‘•’u‚حƒچپ[ƒ_پ[پAƒچپ[ƒ_پ[/ƒAƒ“ƒچپ[ƒ_پ[ƒ‚ƒWƒ…پ[ƒ‹پAƒvƒچƒZƒXƒ‚ƒWƒ…پ[ƒ‹‚©‚ç‚ب‚èپAƒtƒbƒgƒvƒٹƒ“ƒg‚ح•12پ~‰œچs6.5m‚إ‚ ‚éپBٹî”آ”ہ‘—‘¬“x‚حƒ}ƒbƒNƒX400‡o/sپAƒvƒچƒZƒXƒ‚ƒWƒ…پ[ƒ‹‚جƒxپ[ƒXˆ³—ح‚ح3.5پ~10-7torr‚إپA’·‚³1.8m‚جƒٹƒjƒAƒ\پ[ƒXŒ^Niƒ^پ[ƒQƒbƒg‚ً—p‚¢‚éپBگ¬–Œ’†‚جٹî”آ‰·“x‚ح40پژˆب‰؛‚ئ’ل‚پA30•bˆب“à‚إگ¬–Œ‚ھٹ®—¹‚·‚éپB‘O‹L‚ج‚و‚¤‚ةچإ‘ه‚ج“ء’¥‚حپAگ¬–ŒƒŒپ[ƒg‚ً0.1پً/sƒNƒ‰ƒX‚ة‚إ‚«‚邱‚ئپB‚±‚ê‚حپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚بƒXƒpƒbƒ^ƒٹƒ“ƒO‘•’u‚ة”ن‚×1/100ˆب‰؛‚ة“–‚½‚éپB‚±‚ج‚½‚كپANi–§“x‚ً1012پ`1014atoms/cm2‚إگ§Œن‚·‚邱‚ئ‚ھ‚إ‚«‚éپB پ@ژہŒ±‚إ‚حپA‚ـ‚¸گ¬–ŒڈًŒڈ‚ة‚و‚ء‚ؤƒOƒŒƒCƒ“ƒTƒCƒY‚ھ‚ا‚ج‚و‚¤‚ة•د‰»‚·‚é‚©‚ة‚آ‚¢‚ؤ’²‚ׂ½پBژتگ^4‚حSGS poly-Si–Œ‚جSEM‘œ‚إپAگ¬–ŒڈًŒڈ‚ة‚و‚ء‚ؤƒOƒŒƒCƒ“ƒTƒCƒY‚ھ10پ`130ƒتm‚ئ‘ه•‚ةˆظ‚ب‚邱‚ئ‚ھ‚ي‚©‚éپB‚µ‚©‚µپAژہچغ‚ة‚حƒ~ƒjƒ}ƒ€1ƒتm‚جƒOƒŒƒCƒ“‚ة‚·‚邱‚ئ‚à‚إ‚«‚éپB‚آ‚ـ‚èپA—v‹پ‚³‚ê‚éTFT“ءگ«‚ة“K‚µ‚½ƒOƒŒƒCƒ“ƒTƒCƒY‚ة‚·‚邱‚ئ‚ھ‚إ‚«‚éپB

پ@گ}22پA23‚ة“ٌ‘هƒvƒچƒZƒXƒpƒ‰ƒپپ[ƒ^‚إ‚ ‚éٹî”آˆع“®‘¬“xپANiƒ^پ[ƒQƒbƒg‚ض‚ج“ٹ“üƒpƒڈپ[–§“x‚ئƒOƒŒƒCƒ“ƒTƒCƒY‚جٹضŒW‚ًژ¦‚·پB‚آ‚ـ‚èپAˆع“®‘¬“x‚ة”ن—ل‚µ‚ؤƒOƒŒƒCƒ“ƒTƒCƒY‚ھ‘ه‚«‚‚ب‚éˆê•ûپA“ٹ“üƒpƒڈپ[–§“x‚ة”½”ن—ل‚·‚éŒ`‚إƒOƒŒƒCƒ“ƒTƒCƒY‚ھڈ¬‚³‚‚ب‚éپB—ل‚¦‚خˆع“®‘¬“x‚ً30پ“‚©‚ç100پ“‚ةڈم‚°‚é‚ئٹî”آ‚ض‚جƒvƒ‰ƒYƒ}ڈئژثژٹش‚ھ’Z‚‚ب‚èپAa-SiƒvƒٹƒJپ[ƒT–Œڈم‚ة’B‚·‚éNi‚ھŒ¸‚éپB‚±‚جŒ‹‰تپAٹjگ¶گ¬‚جƒVپ[ƒh‚ھŒ¸‚èپAŒ‹‰ت“I‚ةƒOƒŒƒCƒTƒCƒY‚ھ‘ه‚«‚‚ب‚éپBˆê•ûپA“ٹ“üƒpƒڈپ[–§“x‚ً64پ“‚©‚ç136پ“‚ةڈم‚°‚é‚ئپAƒXƒpƒbƒ^ƒٹƒ“ƒO‚³‚ê‚éNi—ت‚ھ‘‚¦‚錋‰تپAƒOƒŒƒCƒ“ƒTƒCƒY‚ھڈ¬‚³‚‚ب‚éپB‚±‚±‚إ’چ–ع‚·‚ׂ«‚حپA“ٹ“üƒpƒڈپ[–§“x‚ًچ‚‚ك‚ؤ‚¢‚‚ئƒOƒŒƒCƒ“ƒTƒCƒY‚جŒ¸ڈŒXŒü‚ھ–Oکa‚·‚邱‚ئ‚إ‚ ‚éپB—ل‚¦‚خپAٹî”آˆع“®‘¬“x29پ“‚إƒpƒڈپ[–§“x‚ً100پ“‚©‚ç136پ“‚ة‘‰ء‚³‚¹‚ؤ‚àƒOƒŒƒCƒ“ƒTƒCƒY‚ح–ٌ3ƒتm‚إ–Oکa‚·‚éپB‚±‚ج‚و‚¤‚ةپA“ٌ‘هƒvƒچƒZƒXƒpƒ‰ƒپپ[ƒ^‚ًƒRƒ“ƒgƒچپ[ƒ‹‚·‚邱‚ئ‚ة‚و‚ء‚ؤڈٹ–]‚جƒOƒŒƒCƒ“ƒTƒCƒY‚ً—eˆص‚ة“¾‚邱‚ئ‚ھ‚إ‚«‚éپB پ@گ}24‚ح1“ْ1–‡SGS Poly-Si‚ً43“ْٹشگ¬–Œ‚µ‚½چغ‚جƒOƒŒƒCƒ“ƒTƒCƒYچؤŒ»گ«‚إپAŒv43–‡‚جٹî”آ‚إƒOƒŒƒCƒ“ƒTƒCƒY‚حپ}5ƒتmˆب“à‚¾‚ء‚½پB‚ـ‚½پA‘و6گ¢‘مٹî”آ–ت“à‚ج90‚©ڈٹ‚ً‘ھ’肵‚½‚ئ‚±‚댋ڈ»‰»—¦‚ح88پ“ˆبڈم‚إپAƒOƒŒƒCƒ“ƒTƒCƒYƒ†ƒjƒtƒHƒ~ƒeƒB‚à10پ“ˆب“à‚¾‚ء‚½پB پ@چإŒم‚ةپA“¯ژذ‚ح‘و8گ¢‘م(2200پ~2500mm)‚â‘و11گ¢‘م(3000پ~3320mm)‚ة‚àƒXƒPپ[ƒ‹ƒAƒbƒv‚ھ—eˆص‚¾‚ئ‚µ‚ؤ‚¢‚éپB ”’گFƒpƒlƒ‹‚âڈئ–¾ƒfƒoƒCƒXŒü‚¯‚ةگV‚½‚بگآگF—سŒُƒzƒXƒg‚ًٹJ”

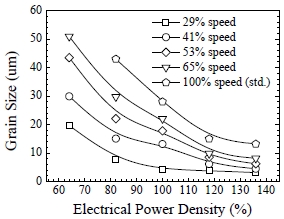

پ@ƒ}ƒeƒٹƒAƒ‹ٹضکA‚إ‚حپA‘نکp‚جIndustrial Technology Research Institute(ITRI)‚ھCBP‚âmCP‚ة‘م‚ي‚éگV‚½‚بگآگF—سŒُƒzƒXƒgچق—؟‚ً’ٌˆؤ‚µ‚½پB پ@گV‚½‚ةچ‡گ¬‚µ‚½‚ج‚حگ}25‚جCzDBSپBTg‚ح133پژپA”M•ھ‰ً‰·“x‚ح380پژ‚ئچ‚‚¢‘د”Mگ«‚ً—L‚·‚éپB‚à‚؟‚ë‚ٌپAƒRƒ“ƒxƒ“ƒVƒ‡ƒiƒ‹‚ب’ïچRڈِ’…–@‚إڈِ’…‚إ‚«پAگ¬–ŒŒم‚حˆہ’è‚بƒAƒ‚ƒ‹ƒtƒ@ƒX–Œ‚ئ‚ب‚éپB‹¤–ً’·‚ً’Z‚‚·‚邽‚كپA“dژq—A‘—گ«ƒWƒxƒ“ƒ]ƒ`ƒIƒtƒFƒ“ٹî‚ئƒzپ[ƒ‹—A‘—گ«ƒJƒ‹ƒoƒ]پ[ƒ‹ٹî‚ً‚آ‚¯‚ؤژOڈdچ€—م‹Nڈَ‘ش‚ً‰ü‘P‚µ‚½پB‚±‚جŒ‹‰تپAFIrpicگآگF—سŒُƒhپ[ƒpƒ“ƒg‚ً—م‹N‚·‚éچغ‚à2.77eV‚ئ—اچD‚بژOڈdچ€—م‹Nڈَ‘ش‚ًژ¦‚·پB

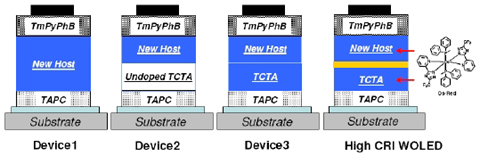

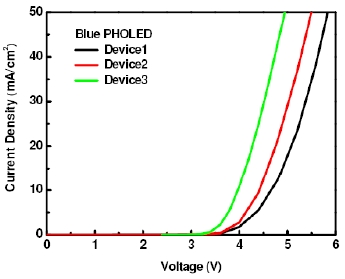

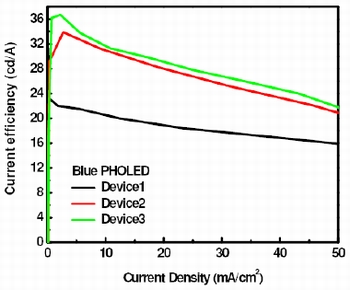

پ@‚»‚ج“ءگ«‚ً•]‰؟‚·‚邽‚كپAFIrpic‚ئ‹¤ڈِ’…‚µپAگ}26‚ج‚و‚¤‚ة‡@ƒfƒoƒCƒX1پFITOƒAƒmپ[ƒh/TAPCƒzپ[ƒ‹—A‘—‘w/FIrpic:HostگآگF”Œُ‘w/TmPyPhB“dژq—A‘—‘w/Cs2CO3ƒoƒbƒtƒ@‘w/AlƒJƒ\پ[ƒhپA‡AƒfƒoƒCƒX2:ITOƒAƒmپ[ƒh/TAPCƒzپ[ƒ‹—A‘—‘w/TCTAƒoƒbƒtƒ@‘w/FIrpic:HostگآگF”Œُ‘w/TmPyPhB“dژq—A‘—‘w/Cs2CO3ƒoƒbƒtƒ@‘w/AlƒJƒ\پ[ƒhپA‡BƒfƒoƒCƒX3:ITOƒAƒmپ[ƒh/TAPCƒzپ[ƒ‹—A‘—‘w/FIrpic:TCTA”Œُ‘w/FIrpic:HostگآگF”Œُ‘w/TmPyPhB“dژq—A‘—‘w/Cs2CO3ƒoƒbƒtƒ@‘w/AlƒJƒ\پ[ƒhپA‚ئ‚¢‚¤3ژي—ق‚جƒfƒoƒCƒX‚ًچىگ»پB‚ـ‚½پAƒzƒXƒgƒtƒٹپ[‚جPO-01‰©گF—سŒُ”Œُƒ†ƒjƒbƒg‚ًƒzپ[ƒ‹—A‘—‘wپ`گآگF—سŒُ”Œُ‘wٹش‚ة‘}“ü‚µ‚½”’گF‘fژq(گ}26‚جHigh CRI WOELD)‚ًچىگ»‚µ‚½پB پ@گ}27‚ةژژچىƒfƒoƒCƒX‚ج“d—¬–§“x-“d—¬Œّ—¦“ءگ«‚ًژ¦‚·پBƒfƒoƒCƒX1‚ح‹P“x1000cd/m2ژ‚ة‚¨‚¯‚é“d—¬Œّ—¦‚ھ21.5cd/A(ٹO•”—تژqŒّ—¦9.2پ“)‚ئ‚à‚ء‚ئ‚à’ل‚©‚ء‚½پB‚±‚ê‚ة‘خ‚µپAƒzپ[ƒ‹—A‘—‘wپ`”Œُ‘wٹش‚ةTCTAƒoƒbƒtƒ@‘w‚ً‘}“ü‚µ‚½ƒfƒoƒCƒX2‚حŒّ—¦‚ھ33.9cd/A(ٹO•”—تژqŒّ—¦14.7پ“)‚ة’B‚µ‚½پBگ}28‚ح“dˆ³-“d—¬–§“x‚جٹضŒW‚إپA“d—¬–§“x20mA/cm2‚ة’B‚·‚é“dˆ³‚حƒfƒoƒCƒX1‚ھ5.2V‚¾‚ء‚½‚ج‚ة‘خ‚µپAƒfƒoƒCƒX2‚ح4.8V‚¾‚ء‚½پB‚±‚ê‚حپATAPC‚جHOMOƒŒƒxƒ‹‚ھ5.5eVپA—سŒُƒzƒXƒg‚جHOMOƒŒƒxƒ‹‚ھ6.0eV‚إ‚ ‚èپA‚±‚جٹش‚ةTCTA(5.7eV)‚ً‘}“ü‚·‚邱‚ئ‚ة‚و‚ء‚ؤƒzپ[ƒ‹’چ“üژ‚جƒGƒlƒ‹ƒMپ[ڈل•ا‚ھ’لŒ¸‚µ‚½‚½‚ك‚إ‚ ‚éپB‚آ‚ـ‚èپAƒLƒƒƒٹƒA‚جچؤŒ‹چ‡ٹm—¦‚ھƒAƒbƒv‚µ‚½‚ئچl‚¦‚ç‚ê‚éپB

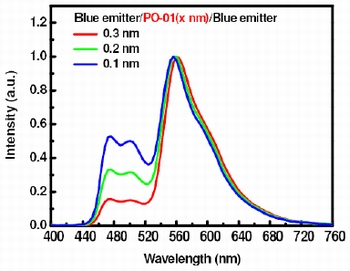

پ@‚ئ‚±‚ë‚إپAˆê”ت“I‚ةگآگF—سŒُ”Œُ‘w‚ًŒْ‚‚·‚é‚ئ‹ى“®“dˆ³‚ھڈمڈ¸‚·‚éˆê•ûپA”–‚‚·‚é‚ئٹO•”—تژqŒّ—¦‚ھ’ل‰؛‚·‚éپB‚±‚¤‚µ‚½ƒgƒŒپ[ƒhƒIƒt‚جٹضŒW‚ً‰ًڈء‚·‚邽‚كپAƒoƒbƒtƒ@‘w‚ة‚àFIrpic‚ًƒhپ[ƒv‚µ‚½ƒ_ƒuƒ‹”Œُ‘w‚ًچج—p‚·‚邱‚ئ‚ة‚µ‚½پB‚±‚ê‚حپAƒ_ƒuƒ‹”Œُ‘w‚جٹE–ت‚إƒLƒƒƒٹƒA‚جچؤŒ‹چ‡‚ھ‹N‚±‚邽‚ك‚إ‚ ‚éپB‚±‚ê‚ھƒfƒoƒCƒX3‚إپA‹P“x1000cd/m2ژ‚جŒّ—¦‚ح33.8cd/A‚ةƒAƒbƒv‚µ‚½‚¾‚¯‚إ‚ب‚پA“d—¬–§“x20mA/cm2‚ة’B‚·‚é“dˆ³‚à3.8V‚ة’ل‰؛‚µ‚½پB پ@گ}29‚ح‰©گF—سŒُ”Œُ‘w‚ًƒCƒ“ƒTپ[ƒg‚µ‚½”’گF‘fژq‚ج“d—¬–§“x-“d—¬Œّ—¦“ءگ«‚إپA‰©گF—سŒُ”Œُƒhپ[ƒpƒ“ƒgPO-01‚ج–ŒŒْ‚ًŒْ‚‚µ‚ؤ‚àŒّ—¦‚ح‚ظ‚ئ‚ٌ‚ا•د‰»‚µ‚ب‚©‚ء‚½پB‚»‚جˆê•û‚إپAPO-01‚ج–ŒŒْ‚ً”–‚‚·‚é‚ئ”Œُ‹“x‚ھŒüڈم‚µ‚½پB‚±‚ê‚ç‚جŒ‹‰تپAŒّ—¦‚ح48.4lm/WپA‹P“x1000cd/m2ژ‚ج“dˆ³‚ح3.6V‚ئ—اچD‚ب“ءگ«‚ھ“¾‚ç‚ꂽپB‚µ‚©‚µپAگF“x‚حxپپ0.37پAyپپ0.48‚ئ•sڈ\•ھ‚¾‚ء‚½پB‚»‚±‚إپA”’گFگF“x‚ً‰ü‘P‚·‚邽‚كپAƒ_ƒuƒ‹گآگF—سŒُ”Œُ‘w‚ةƒIƒXƒ~ƒEƒ€چِ‘جگشگFƒhپ[ƒpƒ“ƒg‚ً‹¤ڈِ’…‚µ‚½پB‚±‚جŒ‹‰تپACRI(color-rendering index)‚ح75‚ةŒüڈم‚µ‚½پB ژQچl•¶Œ£ |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| REMARK 1)Stella’تگM‚حFPDپ•PCBٹضکAƒjƒ…پ[ƒX‚ج–³ڈ’ٌ‹ںƒRپ[ƒiپ[‚إ‚·(ƒXƒeƒ‰پEƒRپ[ƒ|ƒŒپ[ƒVƒ‡ƒ“‚ھFPD‚âPCB‚»‚ج‚à‚ج‚ًگ»•i‰»‚µ‚ؤ‚¢‚é‚ي‚¯‚إ‚ح‚ ‚è‚ـ‚¹‚ٌ)پB 2)‚±‚ج‹Lژ–‚حƒXƒeƒ‰پEƒRپ[ƒ|ƒŒپ[ƒVƒ‡ƒ“ “dژqƒپƒfƒBƒA•”‚ھژوچق‚µ‚ؤ‹Lژ–‰»‚µ‚½‚à‚ج‚إ‚·پB |