|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

SID 09 |

||||||||||||||||||||||||||

最終回である第4回はa-Si TFT、Poly-Si TFTに次ぐ新型TFTとして有機TFTと酸化物TFTをピックアップする。どちらもメインアプリケーションは低温プロセスが求められるフレキシブルディスプレイだが、後者に関してはa-Si TFTを凌駕するハイモビリティを武器にガラス基板製FPDにも応用可能なことが示された。 CNTをソース/ドレインに用いてプリンタブル有機TFTを まず有機トランジスタ関連では、Kyung Hee UniversityとUnidymがCNT(カーボンナノチューブ)をソース/ドレインに用いたプリンタブル有機TFTを報告した14)。

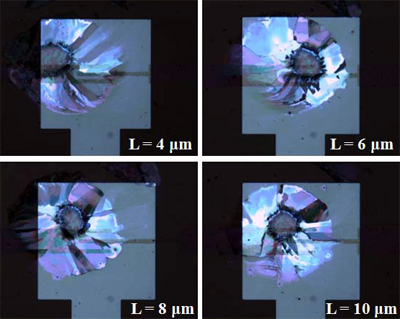

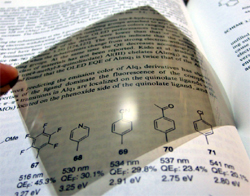

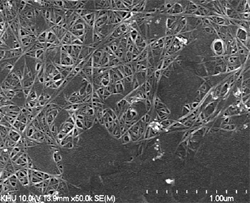

写真27はUnidymのCNT溶液をPENフィルム上に膜厚60nmで塗布した際の写真で、可視光透過率は70%以上、シート抵抗値は80Ω/□である。もちろん、写真27のようにフレキシブル性も保持しており、ウェット法で成膜するため下地に対するステップカバレッジ性も高い。 試作したのはコンベンショナルなボトムゲート・ボトムコンタクト型で、①ガラス基板上にAl-Nd膜をスパッタリング成膜しフォトリソでパターニングしてゲートを形成する、②SiNx膜をプラズマCVD成膜してゲート絶縁膜を形成するとともに、フォトリソでパターニングしてスルーホールを形成する、③CNT溶液を膜厚50nmでスピンコートし、フォトリソ+O2ドライエッチングでパターニングしてソース/ドレインを形成する、④トリクロロベンゼンに溶解させたTIPSペンタセンをIJ印刷して有機半導体層を形成する、といったフローで作製した。写真28はチャネル部の顕微鏡写真で、チャネル長にかかわらずチャネルがTIPSペンタセンで覆われているのがわかる。比較のため、ソース/ドレインとしてAuをスパッタ成膜しフォトリソでパターニングするとともに、半導体層として通常のペンタセンをガスフロー蒸着法で成膜した同じ構造のデバイスも作製した。 チャネル長4μm、チャネル幅100μmのトランジスタの

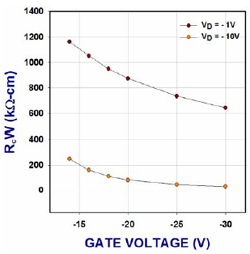

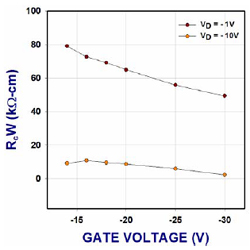

特性を評価したところ、キャリアモビリティは0.15cm2/V・sec、Vthは-3.4V、ON/OFF電流レシオは107だった。これらの値はリファレンスであるAuソース/ドレイン+蒸着ペンタセンデバイスとほぼ同じで、電子ペーパーをドライブするには十分なスペックといえる。 図31、32は半導体層とソース/ドレインの接触抵抗を測定した結果で、TIPSペンタセン半導体層とCNTソース/ドレインの接触抵抗はドレイン電圧-10V、ゲート電圧-20Vの場合8.5kΩ・cmだった。これに対し、リファレンスデバイスの接触抵抗は81.5kΩ・cmと10倍以上だった。前者の結果は、CNTの仕事関数が4.95~5.05eVとTIPSペンタセンのHOMOレベルに近いため良好なコンダクタンスが実現するためである。これに対し、後者ではAuの仕事関数は4.8~5.1eVであるにもかかわらず、Auとペンタセンの熱膨張係数が大きく異なるため、その界面が歪み、結果的に接触抵抗が増大するためと考えられる。 しかし、それでも10倍以上という差は既存の理論では説明できない。そこで、CNTはカーボンネットワーク構造により表面積が広いことも寄与していると推測している。写真29はCNTソース/ドレイン上の一部にTIPSペンタセンを塗布した様子で、TIPSペンタセンは3D構造であるCNTネットワークのブランク部に多く付着するとともに、CNT膜を平滑化しているように見える。これは、ソース/ドレインと半導体層の接触面積が増大していることを意味すると結論づけている。 IGZO-TFTはドライバ回路も基板上にビルトイン可能 一方、ここにきてフレキシブルディスプレイのアクティブ素子として急浮上している酸化物半導体では、半導体エネルギー研究所がアモルファスIGZO(In-Ga-ZnO)を用いてLCDをドライブしたことを報告した15)。IGZO-TFTでLCD、有機ELD、電子ペーパーといったFPDをドライブすること自体はWhat's NEWではないが、特筆されるのはドライバ回路をガラス基板上にビルトインしたことで、IGZO-TFTのさらなるアドバンテージを引き出したといえる。

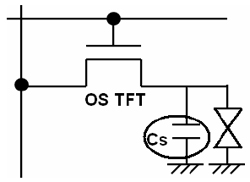

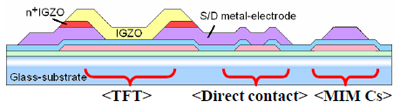

試作したのは図33のボトムゲート・ボトムコンタクト型。IGZO半導体層を最後に形成するためプロセスダメージの心配がないほか、エッチングストッパーも不要など製造工程がシンプル化できるため。さらに、図33のようにLCDではゲートとソース/ドレイン間のゲート絶縁膜をストレージキャパシタに用いることができる。このため、開口率も4%向上する。さらに、図33のゲートとソース/ドレインのダイレクトコンタクトを適用することによりシフトレジスタの個数も12個から6個に半減する。 プロセスフローはゲート、ゲート絶縁膜、コンタクトホールまでをフォトリソで形成した後、①Tiをスパッタリング成膜する、②In2O3:Ga2O3:ZnO(1:1:1)ターゲットを用いてn+ IGZOをスパッタ成膜する、③Tiとn+ IGZOをフォトエッチング法で一括パターニングする、④IGZOをスパッタ成膜し、ソース/ドレイン上に残ったn+ IGZOとIGZOを一括でパターニングする、といったスキームで、最後に350℃でアニール処理した。

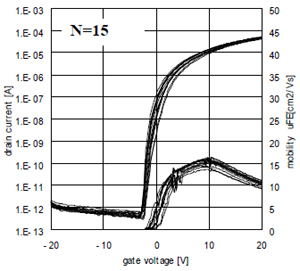

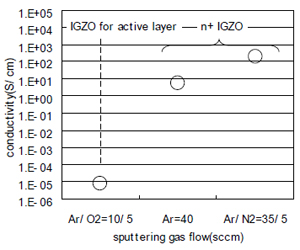

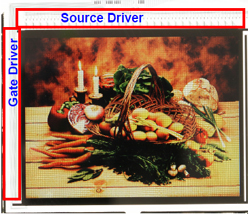

図35はIGZO成膜時におけるガス流量と導電性の関係で、活性層の場合は一般的なAr/O2雰囲気で、一方、n+ IGZOの場合はArガスのみまたはAr/N2雰囲気で成膜すればいいことがわかる。これは、O2ガスをパージしないとIGZO膜中に酸素欠損が発生し、導電性が向上するためと考えられる。この結果、n+ IGZOがソース/ドレインとのコンタクト領域として機能することによりトランジスタ特性が向上する。これは、①O2フリーでTiとn+ IGZOを連続成膜するため、Tiの酸化がなく接触抵抗の増加が抑制される、②n+ IGZO層とIGZO層の界面が安定している、という二つが寄与しているためと思われる。 図36はチャネル長を20μm、チャネル幅を20μmにしたデバイスの特性で、飽和領域におけるモビリティは15.5cm2/V・secと見積もられた。また、Vthは0.42Vときわめて低い値が得られた。そこで、表示エリアの周囲に配置するドライバ回路部のチャネル長を10μmに設定、ゲートドライバ回路、データドライバ回路をガラス基板上にビルトインすることに成功した。写真30は上記のIGZO-TFTでドライブした4.015型LCDで、解像度は99.6dpi、開口率は41.8%となっている。 新たな酸化物半導体で33cm2/V・secというハイスペックが 一方、Electronics and Telecommunications Research Instituteはモビリティ33.5cm2/V・secというハイスペック酸化物TFTを発表。FPDではもっともハードルが高い有機ELDにも適用可能なことを示した16)。

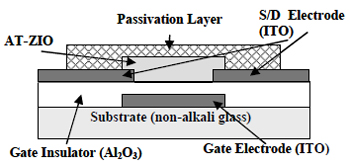

報告したのはAlとSnをドープしたアモルファスZn-In-O(AT-ZIO)。既存のZn-In-Oはモビリティこそ高いものの、化学的安定性かつ電気的安定性に乏しいため、AlとSnをドープしてこうした問題を解消した。 試作したのはコンベンショナルなボトムゲート型で、図37のようにゲートとソース/ドレインにITO、活性層にAT-ZIOを用いることにより透明TFTを実現。ゲート絶縁膜とパッシベーションはAl2O3をALD(Atomic Layer Deposition)法、その他はRFスパッタ法で室温成膜した。なお、各レイヤーのパターニングは既存のフォトリソプロセスを用いた。 気になるAT-ZIO膜はAl2O3-ZnOターゲット、SnO2ターゲット、In2O3-SnO2ターゲットという3種類のターゲットを用いて共スパッタ成膜した。膜はグレインバウンダリーがないアモルファス構造のため安定で、アズデポ後と300℃アニール後のXPS分析でも回折ピークに変化がみられなかった。

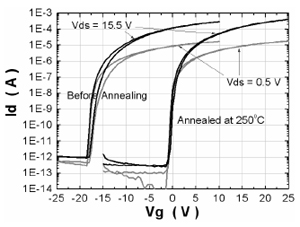

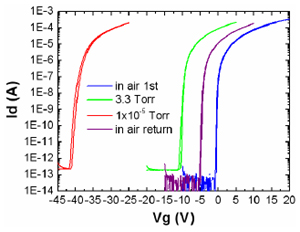

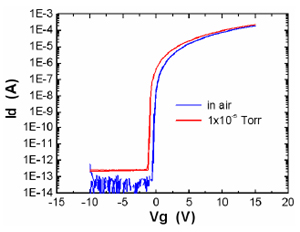

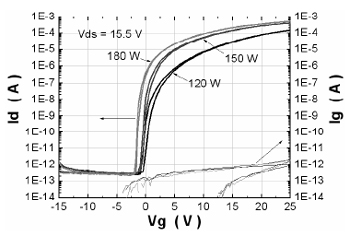

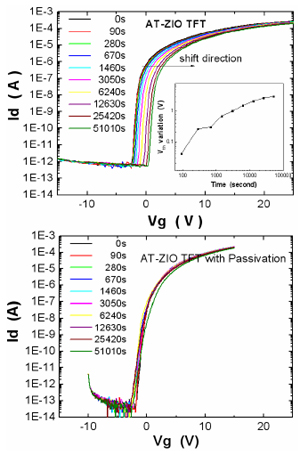

図38はチャネル長20μm、チャネル幅40μmにした際のトランスファー特性で、250℃でのアニール前のモビリティは15.6cm2/V・sec、Vthは-18Vだった。また、比較的大きなヒステリシスが観測された。一方、アニール後はVthが0V近くにまで低下するとともに、ヒステリシスが大幅に抑制された。また、モビリティは24.5cm2/V・sec、ON/OFF電流レシオは108以上(ゲート電圧15.5V時)という高い値が得られた。また、パッシベートせずに2週間以上経過してもモビリティはほとんど低下しなかった。 図39にRFスパッタ成膜時におけるIn2O3-SnO2ターゲットへの投入パワーとトランスファー特性の関係を示す。Al2O3-ZnOターゲットへの投入パワーは300Wに固定したため、膜に対するIn含有量はIn2O3-SnO2ターゲットへの投入パワーの増大にともなって上昇し、投入パワー120Wで16.25cm2/V・sec、150Wで24.55cm2/V・sec、180Wで30.25cm2/V・secというモビリティが得られた。これはInの含有量増加にともなって相対的にSnの含有量が抑制されるためと考えられる。 一方、Al2O3パッシベーション膜を膜厚25nmでALD法で成膜すると、モビリティは33.5cm2/V・secとさらに向上した。また、85℃、85%RH環境で24時間駆動したところ、Vthシフトはわずか0.13Vに過ぎなかった。これはAl2O3パッシベーションによって電気特性が改善されたばかりでなく、耐環境安定性も向上したことを意味する。 ところで、Al2O3以外のパッシベーション膜もテストしところ、いずれのケースでもパッシベート後はVthがマイナス方向にシフトした。これは、真空下における高温プロセスがVthシフトを引き起こすことを示唆する。実際、図40のようにパッシベートレスデバイスの場合、大気環境ではVthが-0.7Vだったが、圧力3.3Torrでは-10.8V、1×10-5Torrでは-41.5Vと大幅にマイナス方向へシフトした。しかし、大気に暴露して1日経過するとVthは-5.1Vに回復した。一方、図40のようにパッシベートしたデバイスは真空環境でもVthシフトはわずかだった。

図41は+20Vのゲート電圧を860分印加した際の安定性を示したもので、パッシベートレスではVthが2.7Vシフトしたのに対し、パッシベートありでは0.8Vにシフト量が抑制された。 上記の結果にもとづいてAT-ZIO駆動の有機ELDを作製した。写真31は試作したモノクロ2.5型QCIFパネルで、ピクセル回路はドライブTFT、スイッチングTFT、ストレージキャパシタというシンプル構成を採用。写真31のように透過率は55%以上と透明ライクなパネルが実現できた。 参考文献

|

||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |