|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

SID 09 |

|||||||||||||||||||||||||||||||||||||||||||||||||||

米San Antonioで開かれたディスプレイ最大の国際学会「The Society for Information Display(SID)」。4回に分けておもなトピックスをレポート。第1回の今回はTFT-LCD関連の発表をクローズアップする。 単層Al-Niをソース/ドレインに用いて4マスクプロセスを

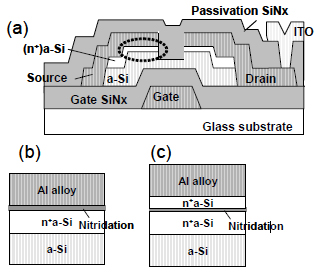

TFTプロセス関連では、神戸製鋼所とコベルコ科研が4マスクプロセスTFT向けとして単層のAl合金をソース/ドレインに用いることを提案した。コンベンショナルなMo/Al/MoやTi/Al/Tiをリプレースする狙いで、1回のウェットエッチングとドライエッチングでパターニングすることができる1)。

従来から同グループは単層ソース/ドレインとしてAl-Ni合金+n+ a-Si表面の窒化処理を提案。今回はn+ a-Si層とAl-Ni合金の相互拡散バリアとしてburied nitridation layer(BNL)と名づけたレイヤーを報告した。 そのTFT作製フローだが、まずゲート電極としてAl-Ni合金膜を膜厚300nmでDCスパッタリング成膜する。次に、SiNx、a-Si、リンをドープしたn+ a-SiをプラズマCVD法で連続成膜する。続いて、N2プラズマ処理によってn+ a-Si膜を窒化処理する。窒化処理は表面を窒化したsurface nitridation layer(SNL)と、新たに考案したBNLを用いた。後者はn+ a-SiをRFパワー密度0.2W/cm2、圧力133Paで窒化処理した後、再度n+ a-Si膜を膜厚5nmで成膜する。つまり、その名のとおり窒化層をn+ a-Si間に埋め込む。 この後、Al-Ni合金を膜厚300nmでスパッタ成膜し、1ウェットエッチング+1ドライエッチングによってパターニングする。具体的には、まずフォトレジストを塗布し、ハーフトーン露光~現像する。この結果、ハーフトーン露光されたチャネル部は現像によっても膜厚が薄くなるだけで、その後のウェットエッチング工程でもチャネル部をプロテクトする。そして、リン酸/硝酸/酢酸エッチャントを用いてチャネル部以外のAl-Ni膜をウェットエッチングする。続いて、チャネル上のAl-Ni膜上に残ったレジスト膜を除去した後、Al-Ni膜とn+ a-Si膜をAr/Cl2/BCl3混合ガスによってドライエッチングしてチャネルを形成する。Al-NiのドライエッチングレートはピュアAlの90%以上とMo/Al/Moとほぼ同等である。また、CDロスも±0.2μmで、エッチング残渣も観察されなかった。

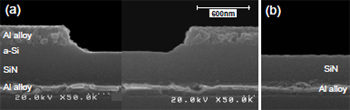

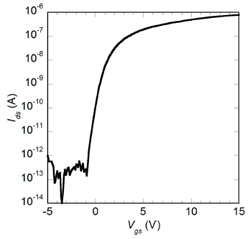

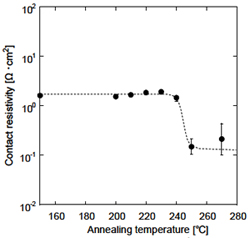

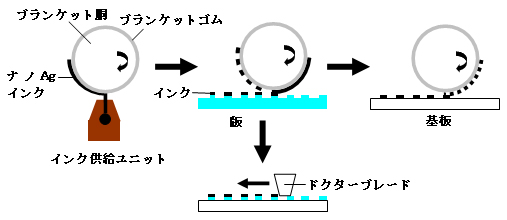

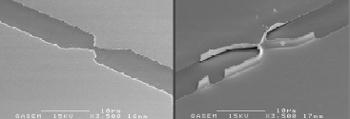

最後に、N2雰囲気において270℃×30分アニール処理する。試作デバイスのチャネル長は10μm、チャネル幅は100μmである。写真1はチャネルのSEM像で、Al-Ni膜がテーパー状にパターニングされチャネルが正確に形成されているほか、(b)のようにドライエッチング後もSiNxに対するダメージがなくAl-Niやa-Siの残渣もないことがわかる。 図2はアニール温度とn+ a-Si~Al-Niの接触抵抗で、アニール温度150~230℃までは接触抵抗は1.3Ω/□だったが、250~270℃では0.15Ω/□と劇的に低下した。この値はMoとn+ a-Siの接触抵抗に匹敵する。ただ、これ以上アニール温度を上げたり処理時間を長くすると接触抵抗が不安定になり、n+ a-SiとAl-Niの相互拡散の危険が高まる。図3はTFTの特性で、オフ電流は10-13A、ON/OFF電流レシオは106と良好な特性が得られた。 昨年の「SID 08」で反転オフセット印刷法によってレジストを印刷したTFT-LCDを発表したLG Display。今回はナノメタルインクを用いてゲート電極をダイレクト印刷したことを報告した2)。 図4のように反転オフセット印刷法はブランケット胴の全面にコートしたインクをパターニングされた凸版に転写し、残ったインクをワークに転写する。コンベンショナルなオフセット印刷が版上にあるインクをブランケット胴に転写するのに対し、余分なインクを版に転写除去する点が決定的に異なる。

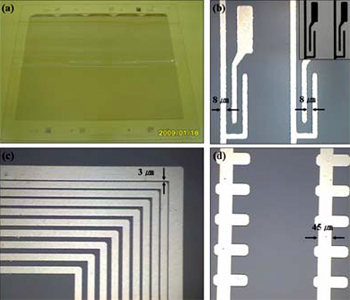

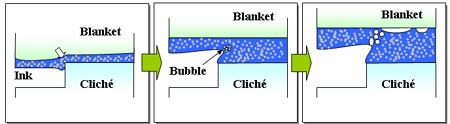

写真2は粒径約50nmのナノAgインクを印刷した例で、線幅8μm、ギャップ3μm以下というファインパターンが得られた。これはナノAgを用いたためで、図5のように版とブランケット胴が接触する際にきわめて微小なバブルが発生し、版とブランケット胴双方からの“糸引き現象”が発生せずに100%転写が可能になる。この結果、高精度&ファインパターニングが実現する。また、写真2-(b)のように電極ライン上にもピンホール欠陥が観察されなかった。

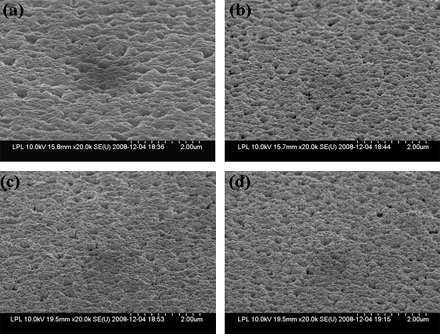

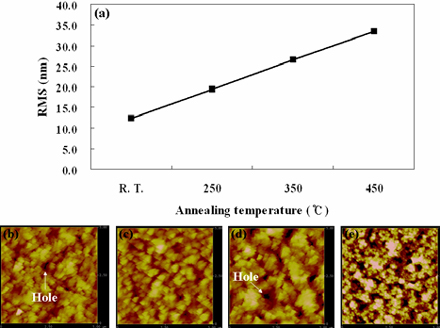

いうまでもなく、印刷膜厚と焼成温度にともない比抵抗は変化し、450℃×10minで焼成した場合、比抵抗4.5μΩ・cmが得られた。これはバルク抵抗の2.8倍に当たり、インクに含まれる樹脂成分や溶剤成分が一部膜に残留しているためと考えられる。写真3は膜厚を650nmにして焼成温度を変化させた際のSEM像で、グレイン間のホール密度は焼成温度によって変化する。写真4は焼成温度とAFM像の関係で、焼成温度が高くなるにつれてホール密度と表面粗度が高くなる。TFTのゲートに用いる場合、その表面平滑性は上部に形成されるSiNxゲート絶縁膜の表面平滑性に大きな影響を与え、a-SiとSiNx間のキャリアパスをブロックするため、許容比抵抗以内の範囲で焼成温度を低温化する必要があると考えられる。 試作したTFTの特性だが、キャリアモビリティは0.16cm2/V・sec、ON/OFF電流レシオは1.5×106、Vthは3Vだった。これは、スパッタリング成膜したAl-Ndゲートを用いた場合に比べ低い。これは、ゲートの表面平滑性低下にともなってキャリアの移動が抑制されたためと考えられる。

MILCによるPoly-Si化で最大の問題をブレークスルー

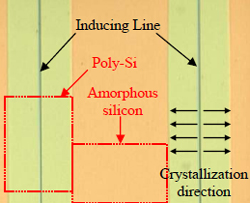

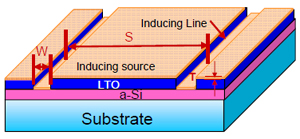

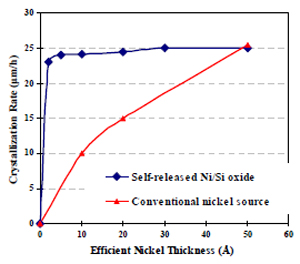

低温Poly-Si TFT-LCD関連では、Hong Kong University of Science and TechnologyとNankai Universityがa-Siプリカーサの新たなPoly-Si化法として検討されているMetal-Induced Lateral Crystallization(MILC)について発表した。MILCで問題となっているPoly-Si膜内におけるNi残留量を低減する狙いで、Poly-Si化を促進するメタル材料として従来のピュアNiに代わってNi-Si酸化物を用いることを提案した3)。 熱酸化SiO2膜付きの4インチシリコンウェハーを用いて、まずLP-CVD法でa-Si膜を膜厚50nmで成膜。次に、酸化物を膜厚100nnmで低温成膜し、フォトウェットエッチング法でパターニングした。ここでエッチングするラインをinducing lines(IL)と呼ぶことにする。最後に、セルフリリース(SR)Ni:Si酸化物ターゲットを用いてAr:O2(200:1)ガス雰囲気においてベタでスパッタリング成膜した。ターゲットの組成比率はNi:Si=1:9である。比較のため、ピュアNiを電子ビーム蒸着したサンプルも作製した。 成膜後、N2雰囲気において590℃×1時間アニールしPoly-Si化した。この際、ILの幅(W)、スペース(S)、膜厚(T)が結晶化レートに多大な影響を及ぼす。結晶化はILの周辺から起こり、写真5のようにアニール時間の経過にともなって結晶化が進行する。つまり、Poly-Siの水平方向成長ディメンジョンはアニール時間によって決まる。 図7はILの幅を30μm、スペースを5000μmに固定した際の結晶化レートと膜厚(T)の関係で、セルフリリースNi:Siの結晶化レートはピュアNiの10倍に達した。こうした大きな差ができたのはその結晶化成長メカニズムが異なるため。前者は膜厚が0.4nm以上になると結晶化レートがマックスになって安定する。これに対し、後者は膜厚の増加にともなってほぼリニアに結晶化レートが向上する。

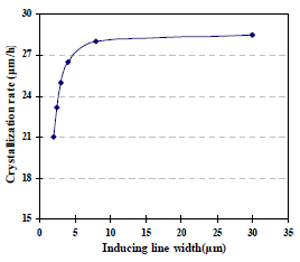

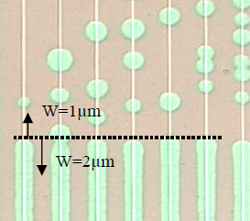

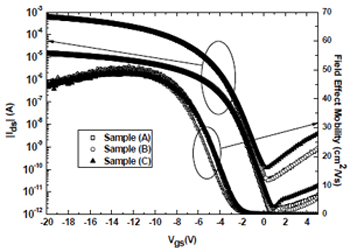

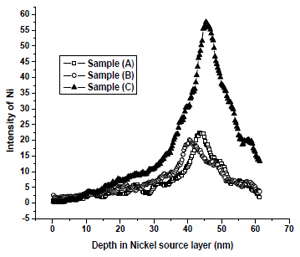

図8はSを60μm、Tを2nmに固定した際のILの幅と結晶化レートの関係で、Wが広くなると結晶化レートが向上し、8μmで飽和することがわかる。これは結晶化には一定量のNiが必要なためと考えられる。いうまでもなくa-Siとのダイレクトコンタクト面積はWによって決まり、Wが広いほどNi原子が拡散しa-Siの結晶化が促進されて結晶化レートが向上する。そして、Wを8μm、Sを60μmにすると、アニール温度590℃で結晶化レートが最大となり飽和する。さらに興味深いのは、写真6のようにW=2μmではW=1μmに比べ大幅に結晶化領域が広くなることで、後者ではグレインが円形状にしか成長しなかった。一方、Sの長さも結晶化レートを左右し、Sが狭いとWが相対的に広くなるため結晶化レートが向上する。 図9はサンプルA(投入パワー7Wで3分スパッタ成膜したセルフリリースNi:Si)、サンプルB(パワー6Wで60分スパッタ成膜したセルフリリースNi:Si)、サンプルC(EB蒸着したピュアNi)という3種類を590℃×2時間アニールしてPoly-Si化した際のTOF-SIMS測定結果で、サンプルA、BともCに比べ残留Niが2倍以上少なかった。これらの結果、セルフリリースNi:Siを用いるとPoly-Si膜中におけるNiの残留が大幅に低減することが確認された。実際に低温Poly-Si TFTを試作し特性を評価したところ、セルフリリースNi:Siデバイスはoff電流、リーク電流とも減少した。これに対し、ピュアNiデバイスはoff電流、リーク電流ともセルフリリースNi:Siの4倍以上に達した。 MVAパネルのITO電極をレーザーアブレーションで

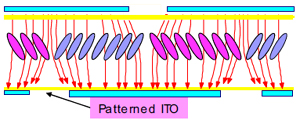

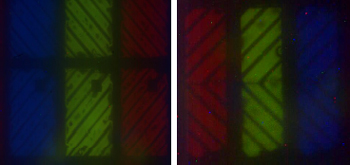

コンベンショナルなフォトリソに代わる技術としてレーザードライエッチング法によるITOパターニング技術を発表したのがSamsung Electronicsらの研究グループ。CF上にストライプ状のITOパターンを設けるPVAパネル向けで、マルチドメインのフリンジ領域を形成するためITOをレーザーアブレーションによってダイレクトパターニングした4)。 小型マスクを介してエキシマレーザービ

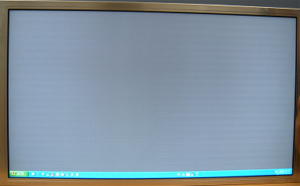

ーム(波長248nm)を照射してITO膜をアブレーション除去する仕組みで、実験にはシングルヘッド搭載の第8世代対応装置(2200×2500㎜)を用いた。エッチング幅は4~11μmで、基板温度を室温と高温にして比較テストした。写真7のように高温処理したところ残渣のない良好なパターニング性が確認できたが、ITOパターンに沿って一部にパターニングムラが観測された。ただし、これは光学的には問題なく、写真8のように従来のウェットエッチング法でパターニングしたITOパターンと比較してもほとんど変わらず、表1のように光学特性の違いも観測されなかった。また、下層であるオーバーコート層へのダメージもなかった。 ただし、レーザービームショット毎によるビーム形状、幅、長さの不均一性によって、マクロ的には試作した23型PVAパネルでは写真9のようにつなぎ目が観測された。このため、“Gradual stitch techniques”と名づけた独自技術によりマクロムラを低減したとしている。

考文献

|

|||||||||||||||||||||||||||||||||||||||||||||||||||