|

STELLA捠怣偼噴僗僥儔丒僐乕億儗乕僔儑儞偑塣塩偟偰偄傑偡丅 |

廐婫墳梡暔棟妛夛(9寧17乣20擔) |

||||||||

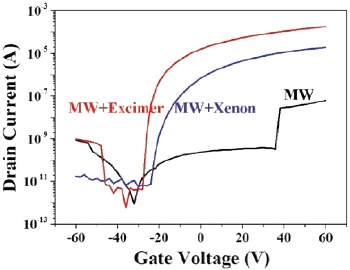

丂9寧17乣20擔丄杒奀摴戝妛偱奐偐傟偨乽戞75夞墳梡暔棟妛夛廐婫妛弍島墘夛乿丅梊峞廤傪儀乕僗偵FPD傗TFT偵娭偡傞僩僺僢僋僗傪僺僢僋傾僢僾偡傞丅 儅僀僋儘攇徠幩偲岝徠幩偱揾晍宆巁壔暔敿摫懱枌傪掅壏從惉 丂a-Si TFT丄掅壏poly-Si TFT偵師偖戞3偺FPD梡TFT偲偟偰昡壙偑妋棫偝傟偨巁壔暔TFT偱偼丄崱夞揾晍宆僨僶僀僗偺曬崘偑憡師偄偩丅廃抦偺傛偆偵丄揾晍宆巁壔暔TFT偼巁壔暔敿摫懱枌偺從惉壏搙偑崅偄偙偲偑幚梡壔傪朩偘偰偄傞偨傔偱丄嶻嬈媄弍憤崌尋媶強(嶻憤尋)偼怴偨側從惉僾儘僙僗偵傛偭偰從惉壏搙傪掅壏壔偡傞偲偲傕偵抁弅偡傞偙偲偵惉岟偟偨丅 丂恾1偼儅僀僋儘攇徠幩亄僄僉僔儅儔儞僾傑偨偼Xe僼儔僢僔儏儔儞僾偱岝徠幩偟偨TFT偺摿惈偱丄儅僀僋儘攇從惉偺傒偱偼ON揹棳偑10-7A偲旕忢偵掅偐偭偨偺偵懳偟丄岝徠幩傪暪梡偡傞偲ON揹棳偑寑揑偵憹壛偟偨丅傑偨丄OFF揹棳傕10-12A戜偲傎偲傫偳曄壔偣偢丄儅僀僋儘攇徠幩偺傒偵斾傋TFT摿惈傕夵慞偝傟偨丅 億僗僩IGZO-TFT偲偟偰InWO-TFT偑晜忋

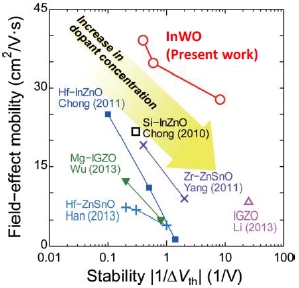

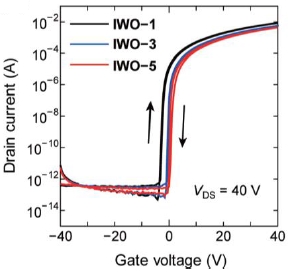

丂懠曽丄暔幙丒嵽椏尋媶婡峔偼恀嬻惉枌側偑傜150亷埲壓偺掅壏僾儘僙僗偱嶌惢偟偨傾儌儖僼傽僗InWO-TFT偵偮偄偰曬崘偟偨丅 丂嬶懱揑偵偼丄InO偵僞儞僌僗僥儞(W)傪揧壛偟偨InWO僠儍僱儖憌傪擬巁壔枌晅偒僔儕僐儞婎斅忋偵DC儅僌僱僩儘儞僗僷僢僞儕儞僌朄偱惉枌丅偙偺屻丄揹巕價乕儉忲拝朄偵傛偭偰Au/Ti僜乕僗丒僪儗僀儞揹嬌傪宍惉偟丄儃僩儉僎乕僩丒僩僢僾僐儞僞僋僩峔憿僨僶僀僗傪嶌惢偟偨丅嵟屻偵丄150亷偱戝婥拞傾僯乕儖偟偰揹嬌乣僠儍僱儖娫偺僐儞僞僋僩惈傪崅傔偨丅 丂恾2偼僞乕僎僢僩偺WO3揧壛検(1丄3丄5wt亾)偲TFT摿惈偺娭學偱丄W揧壛検偺憹壛偵偲傕側偄棫偪忋傝揹埑偑惓偵僔僼僩偟丄IWO-5偱僲乕儅儕乕僆僼傪払惉偟偨丅偙偺IWO-5偵懳偟偰VGS亖亅20V偺晧僎乕僩僶僀傾僗傪報壛偟偨偲偙傠丄5000昩娫偱嚈Vth亖亅0.1V偲偄偆椙岲側僶僀傾僗僗僩儗僗懴惈偑摼傜傟偨丅偮傑傝丄僉儍儕傾儌價儕僥傿傪戝偒偔懝側偆偙偲側偔崅偄僶僀傾僗僗僩儗僗埨掕惈偑摼傜傟偨(恾3)丅偙傟偼丄W偺帩偮崅偄巁慺夝棧僄僱儖僊乕偲崅偄尨巕壙偑嬱摦椡偲埨掕惈偺椉棫偵婑梌偡傞偨傔偲峫偊傜傟傞丅 塼懱僔儕僐儞仌儗乕僓乕傾僯乕儖傪梡偄偰揾晍宆掅壏poly-Si枌傪嶌惢

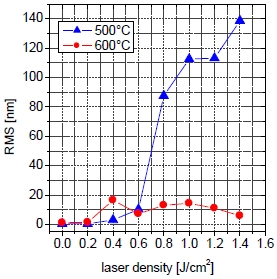

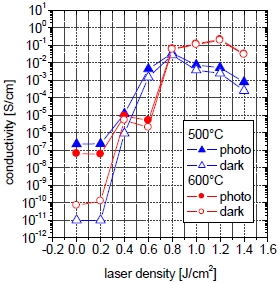

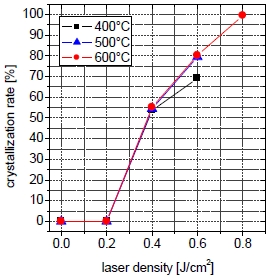

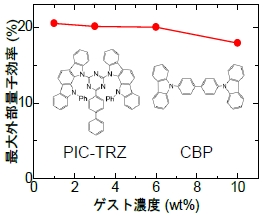

丂堦曽丄掅壏倫oly-Si TFT岦偗偱傕杒棨壢妛媄弍戝妛堾戝妛偑撈帺偺塼懱僔儕僐儞傪梡偄偨揾晍宆僨僶僀僗傪曬崘偟偨丅 丂幚尡偱偼丄傑偢尨椏偵塼懱僔儕僐儞傪梡偄偰戝婥埑擬CVD朄偵傛偭偰僈儔僗婎斅忋偵a-Si:H枌(枌岤100nm)傪惉枌偟偨丅塼懱尨椏a-Si:H枌拞偺悈慺検偑寢徎壔偵梌偊傞塭嬁傪挷傋傞偨傔丄恀嬻拞偵偍偄偰弖娫擬張棟(RTA:Rapid thermal anneal)偵傛偭偰扙悈慺張棟偟丄悈慺娷桳検偺堎側傞僒儞僾儖傪3庬椶(400亷 H:20亾丄500亷 H:10亾丄600亷 H:0.1亾)梡堄偟偨丅偙傟傜偵僌儕乕儞儗乕僓乕(Yb:YA丄攇挿515nm)傪徠幩偟偰寢徎壔偝偣偨丅偙偺嵺偺僄僱儖僊乕枾搙偼0乣1.4J/cm2偱偁傞丅 丂恾4偵摼傜傟偨poly-Si敄枌偺寢徎壔棪傪帵偡丅400亷丄500亷從惉僒儞僾儖偱偼姰慡偵寢徎壔偡傞慜偵悈慺傾僽儗乕僔儑儞偑婲偒偨偑丄600亷從惉僒儞僾儖偱偼傾僽儗乕僔儑儞偡傞偙偲側偔寢徎壔偟偨丅恾5偵500亷丄600亷從惉僒儞僾儖偺擇忔暯嬒慹偝(RMS)偲儗乕僓乕枾搙偺娭學丄恾6偵埫帪丄岝徠幩帪偵偍偗傞摫揹棪偲偺娭學傪帵偡丅500亷從惉僒儞僾儖偱偼丄儗乕僓乕枾搙偺憹壛偵偲傕側偄RMS偺憹壛偑傒傜傟偨丅傑偨丄摫揹棪偼儗乕僓乕枾搙偑0.8J/cm2帪偵僺乕僋傪帵偟丄偦偺屻尭彮偡傞偙偲偑傢偐偭偨丅偙傟偼丄Si枌偼悈慺傾僽儗乕僔儑儞偵傛偭偰億乕儔僗側枌偲側傝丄摫揹棪偺尭彮偵偮側偑偭偨偨傔偱偁傞丅偝傜偵丄600亷從惉僒儞僾儖偱偼儗乕僓乕枾搙傪憹壛偝偣偰傕昞柺暯妸惈偑曐偨傟偰偍傝丄儗乕僓乕枾搙1.2J/cm2帪偵2亊10-1S/cm偲崅偄摫揹棪偑摼傜傟偨丅 桳婡EL偱偼僪乕僷儞僩擹搙傪戝暆偵掅尭壜擻側椨岝儂僗僩偑 丂桳婡EL偱偼丄搶嫗棟壢戝妛偲NHK曻憲媄弍尋媶強偑儘乕僐僗僩壔偑梕堈側掅暘巕椨岝僨僶僀僗傪曬崘偟偨丅偙偙偱偄偆儘乕僐僗僩壔偲偼崅壙側Ir嶖懱僪乕僷儞僩偺巊梡検傪寑揑偵嶍尭偟偨偙偲偱丄椨岝儂僗僩偵TADF嵽椏傪梡偄傞偙偲偵傛傝僪乕僷儞僩擹搙傪尭傜偟偰傕岠棪丒庻柦摿惈偲傕掅壓偟側偄偲偄偆丅 丂崱夞嶌惢偟偨慺巕偼ITO傾僲乕僪/PEDOT儂乕儖拲擖憌/兛-NPD儂乕儖桝憲憌/HTLB-2(娭搶壔妛惢)/儂僗僩:Ir(mppy)3椢怓敪岝憌/TPBI揹巕桝憲憌/LiF僶僢僼傽憌/Al僇僜乕僪偲偄偆峔惉丅儂僗僩偲偟偰TADF嵽椏偱偁傞2-biphenyl-4,6-bis(12-phenylindolo[2,3-a]carbazol-11-yl)1,3,5-triazine(PIC-TRZ)傪梡偄丄僪乕僷儞僩擹搙傪1丄3丄6丄10wt亾偵偟偰摿惈傪昡壙偟偨丅傑偨丄儕僼傽儗儞僗偲偟偰PIC-TRZ偲摨條丄僇儖僶僝乕儖暘巕崪奿傪傕偮CBP傪儂僗僩偵梡偄偨慺巕(僪乕僷儞僩擹搙6wt亾)傕嶌惢偟偨丅 丂恾7偵PIC-TRZ慺巕偺嵟戝奜晹検巕岠棪偺僪乕僷儞僩擹搙摿惈傪帵偡丅擹搙6wt亾偺応崌丄嵟戝奜晹検巕岠棪偼20亾丄弶婜婸搙1000cd/m2帪偺婸搙敿尭庻柦偼栺8600帪娫偩偭偨丅偙傟偵懳偟丄CBP慺巕偺嵟戝奜晹検巕岠棪偼20亾丄婸搙敿尭庻柦偼栺1500帪娫偩偭偨丅偮傑傝丄PIC-TRZ傪儂僗僩偵梡偄傞偙偲偵傛傝栺6攞偺挿庻柦偑摼傜傟偨丅

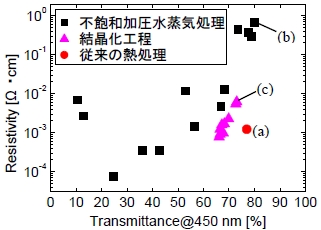

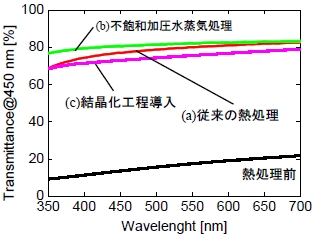

丂傑偨丄儂僗僩偵PIC-TRZ傪梡偄偨応崌丄僪乕僷儞僩擹搙偵埶懚偣偢崅偄奜晹検巕岠棪偑摼傜傟偨丅偙傟偼丄儂僗僩偵PIC-TRZ傪梡偄傞偙偲偵傛傝岠棪揑側儂僗僩-僎僗僩娫偺僄僱儖僊乕堏摦偑婲偙傞偨傔偲峫偊傜傟傞丅偝傜偵丄摨條側僇儖僶僝乕儖暘巕崪奿傪帩偮偵傕娭傢傜偢庻柦偵戝偒側嵎偑弌偨偙偲偐傜丄儂僗僩偵PIC-TRZ偲CBP傪梡偄偨応崌偱偼儂僗僩-僎僗僩娫偺僄僱儖僊乕堏摦夁掱偑堎側傞偲峫偊傜傟傞丅偔傢偊偰丄儂僗僩偵PIC-TRZ傪梡偄偨僪乕僷儞僩擹搙1wt亾偺慺巕偼婸搙敿尭庻柦1枩帪娫埲忋偑摼傜傟偨丅 僼儗僉僔僽儖僨傿僗僾儗僀岦偗偲偟偰140亷偱寢徎壔偡傞ITO枌傪採埬 丂摟柧揹嬌偲偟偰峀偔梡偄傜傟傞ITO娭楢偱偼丄搶嫗棟壢戝妛偲暯嶳惢嶌強偺尋媶僌儖乕僾偑僼儗僉僔僽儖僨傿僗僾儗僀岦偗偲偟偰掅壏僾儘僙僗偱寢徎壔偡傞ITO枌傪採埬偟偨丅 丂幚尡偼丄僒僼傽僀傾婎斅忋偵揹巕價乕儉忲拝朄偵傛傝ITO枌傪枌岤50nm偱忲拝偟偨丅枌偺摟夁棪偼13亾(@450nm)丄掞峈棪偼1亊10-2兌m偱偁傞丅偙偺屻丄3庬椶偺擬張棟傪峴偭偰摟柧摫揹枌壔傪帋傒偨丅嬶懱揑偵偼丄廬棃偺擬張棟(戝婥暤埻婥偱700亷亊3暘)傪峴偆偲丄摟夁棪偼77亾(@450nm)丄掞峈棪偼1亊10-3兌m偵曄壔偟偨丅偙傟偵懳偟丄崅幖搙丒崅埑椡傪壛偊傞晄朞榓壛埑悈忲婥張棟(栺3婥埑偱140亷丄幖搙85亾亊5帪娫)偵傛偭偰擬張棟偟偨偲偙傠丄摟夁棪偼80亾(@450nm)偵傑偱払偟偨偑丄掞峈棪偼10-1兌m戜偵傑偱忋徃偟偨丅偦偙偱丄晄朞榓壛埑悈忲婥張棟慜偵寢徎壔岺掱(戝婥埑偱140亷丄幖搙3亾亊5帪娫)傪憓擖偟偨偲偙傠丄掞峈棪偼10-3兌m慜屻傑偱掅壓偟偨丅偮傑傝丄晄朞榓壛埑悈忲婥偵傛傞嫮椡側巁壔椡偵傛偭偰ITO偵懚嵼偡傞巁慺寚懝傪杽傔傞偙偲偑偱偒摟夁棪偑岦忋偡傞偲偲傕偵丄寢徎壔岺掱偵偍偗傞擬偵傛偭偰寢徎偺尨巕攝楍偑惍偊傜傟掞峈棪偑掅壓偟偨傢偗偱偁傞丅

嶲峫暥專 |

| REMARK 1)Stella捠怣偼FPD仌PCB娭楢僯儏乕僗偺柍彏採嫙僐乕僫乕偱偡(僗僥儔丒僐乕億儗乕僔儑儞偑FPD傗PCB偦偺傕偺傪惢昳壔偟偰偄傞傢偗偱偼偁傝傑偣傫)丅 2)偙偺婰帠偼僗僥儔丒僐乕億儗乕僔儑儞 揹巕儊僨傿傾晹偑庢嵽偟偰婰帠壔偟偨傕偺偱偡丅 |

|