|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

秋季応用物理学会(9月16~20日) |

||||||||||||||||||||||||||||

9月16~20日、同志社大学で開かれた「第74回応用物理学会秋季学術講演会」。予稿集をベースにトピックスをピックアップする。 光透過性カソードにAl/MoOx/IZOを用いてIZO成膜時のスパッタダメージを低減

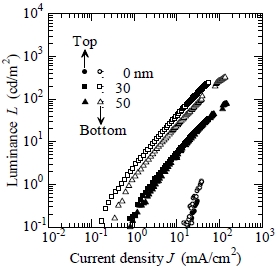

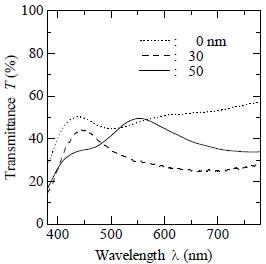

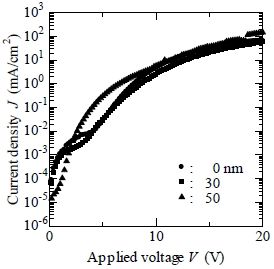

まず有機ELでは、富山大学の研究グループがトップエミッション構造有機ELや透明有機ELの光透過性カソードとしてメタル/MoOx/IZOの3層構造を提案した。 実験で作製したデバイスはITOアノード(膜厚160nm)/α-NPDホール輸送層(50nm)/Alq3緑色発光層兼電子輸送層(50nm)/LiFバッファ層(1nm)/Al(5nm)/MoO3(Xnm)/IZO(120nm)光透過性カソードという構造。Al/MoO3/IZO光透過性カソードのうち、Al膜を5nmと極薄化することにより半透過性を確保した。また、MoO3はIZO膜をスパッタリング成膜する際のプラズマから有機層を保護するプロテクターレイヤーとして機能する。 図1にデバイスの電流密度-電圧特性、図2に電流密度-輝度特性を示す。リファレンスとして作製したMoO3レスデバイスは最高輝度が1cd/m2前後ときわめて低かったが、Al/IZO界面にMoO3を挿入すると特性が劇的に向上した。これは、上記のようにMoO3を挿入するとIZOスパッタ成膜時のスパッタダメージが低減されるためと考えられる。図3はデバイスの光透過率で、Alq3の発光ピーク波長510nmにおける透過率はMoO3膜厚0nmで45%、30nmで33%、50nmで44%だった。

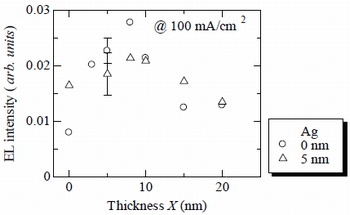

局在表面プラズモン共鳴によって有機ELの発光強度を向上 富山大学は、金属微粒子を用いた局在表面プラズモン共鳴によってEL発光強度を高めるというユニークな研究成果も報告した。 周知のように、AuやAgなどの金属微粒子に光を照射すると局在表面プラズモン共鳴によって金属中の電子が振動し、特異な光吸収の発現や金属微粒子表面近傍で電場増強することが知られる。そこで、ITO透明電極上に島状Ag蒸着膜(i-Ag)を設けた有機ELを作製した。 実験では、まずITO膜付きガラス基板上に膜厚5nm相当のAgを真空蒸着し、N2雰囲気で200℃×15分ベークした。この結果、Agが凝集し、直径20~60nmの島状粒子が形成される。次に、赤色発光材料であるテトラフェニルポルフィリン(TPP)、α-NPD、BCP、LiF/Alを真空蒸着した。素子構造はITO(160nm)/i-Ag(0.5nm)/α-NPD(Xnm)/TPP(5nm)/α-NPD(30nm)/BCP(70-Xnm)/LiF(1nm)/Al(70nm)である。

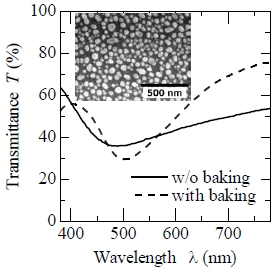

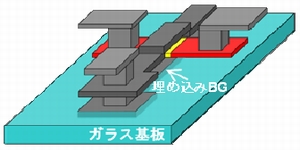

図4はITO/i-Agの透過スペクトルと表面SEM像で、ベーク後の透過スペクトルには局在表面プラズモン共鳴による吸収のため透過率に谷がみられた。図5はα-NPD由来の450nmの発光強度に対するTPP由来の650nmの発光強度比で、X=8nmで最大となり、その後、Xnmの増加とともに減少した。これはi-Agによる局在表面プラズモン共鳴効果によってTPPの蛍光が増強したためと考えられる。 自己整合埋め込み型メタルダブルゲートで低温Poly-Si TFTを高性能化 その作製プロセスだが、まずガラス基板に反応性イオンエッチング(RIE)によってボトムメタルゲート用の凹構造を形成する。この後、W膜をスパッタリング成膜して凹部に埋め込む。続いて、CMPにより余分なWを除去してボトムメタルゲートを形成する。次に、ボトムゲート酸化膜、a-Si膜をプラズマCVD成膜する。そして、a-Siプリカーサ膜にDPSS CWレーザラテラル結晶化(CLC)処理を施してpoly-Si化する。この後、トップゲート酸化膜をCVD成膜、続いてW膜をスパッタ成膜する。続いて、ボトムゲートをマスクにした自己整合技術によりトップメタルゲートを形成し、イオン注入を行う。最後に、層間絶縁膜をCVD成膜して電極を形成する。これら一連のプロセスにおける最高温度は550℃である。

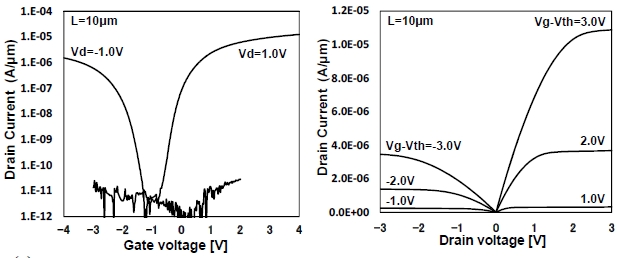

図7はゲート長10μmデバイスのトランスファー特性とアウトプット特性で、n型、p型ともに鋭い立ち上がりが確認できた。また、線形領域におけるモビリティも高い値が得られた。こうした結果はガラス基板上の低電圧動作CMOS回路の実現可能性を示すといえる。 エッチングストッパー成膜条件でIGZO-TFTの特性を制御

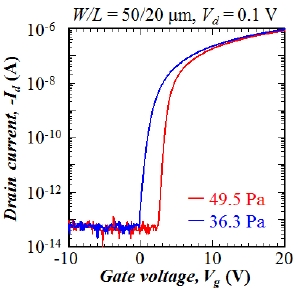

新世代TFTとしての評価が確立したIGZO(In-Ga-Zn-O)-TFTでは、高知工業大学の研究グループがコンベンショナルなエッチングストッパー付きボトムゲートa-IGZO-TFTのエッチングストッパー成膜条件とデバイス特性の関係を報告した。 周知のように、エッチングストッパーはSiOxなどのSi系膜をプラズマCVD成膜するが、成膜時のプラズマダメージによってチャネルとエッチングストッパー(バックチャネル)の界面に酸素欠陥が生成される。そこで、エッチングストッパー成膜条件がバックチャネル欠陥準位とデバイス特性・信頼性に与える影響について調べた。 実験では、シラン(SiH4)と亜酸化窒素(N2O)を原料ガスに用いてSiOxエッチングストッパーをプラズマCVD成膜した。そして、このエッチングストッパーを用いたa-IGZO TFT を作製した。

図8にN2Oガス分圧49.5Paと36.3Paで成膜したSiOx絶縁膜をエッチングストッパーに用いたa-IGZO TFTの線形領域におけるトランスファー特性、表1にトランスファー特性から抽出したTFT特性を示す。N2Oガス分圧を49.5Paから36.3Paに減少させたところ、キャリアモビリティはほとんど変化しなかったのに対し、サブスレッショルド・スイング(S)は0.3V/decから0.5V/decに増大し、立ち上がり電圧(ドレイン電流1nA時のゲート電圧)も3.7Vから1.7Vへネガティブシフトした。この結果から、SiOx成膜時のN2Oガス分圧がバックチャネル欠陥準位に影響を与え、Sファクターの増大、そして立ち上がり電圧のネガティブシフトにつながったと推察できる。また、エッチングストッパー成膜条件によってa-IGZO TFTのVthが制御可能であることを示唆している。 マイクロ波加熱でIGZOゾルを高速硬化

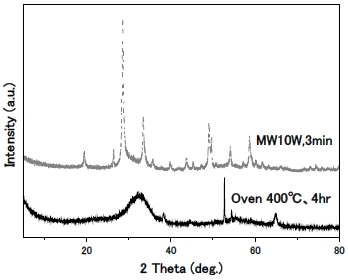

一方、産業技術総合研究所は塗布型酸化物TFT向けとしてマイクロ波加熱焼成法を提案した。 周知のように、マイクロ波加熱は短時間で均一な加熱ができるため、既存のオーブン加熱に比べプロセス時間が短縮できる。また、選択加熱が可能なため、フレキシブルTFTのサブストレートに使われるプラスチックフィルムが損傷することがない。今回は基板上にスクリーン印刷したIGZO前駆体ゾルをXRDによって焼成状態を評価した。 IGZO前駆体ゾルはIn、Ga、Znの各硝酸塩、尿素およびアルコールアミンを用いて合成した。この前駆体ゾルをO2プラズマ処理によって親水化した酸化膜付きシリコン基板表面にスクリーン印刷した。その後、オーブン加熱では400℃×4時間、マイクロ波加熱(2.45GHz)では10W×3分、空気中で焼成した。 図9に焼成後のXRD測定結果を示す。オーブン加熱ではアモルファスなスペクトルが観察されたのに対し、マイクロ波加熱ではIGZOの結晶化が観察された。このため、マイクロ波加熱は短時間で効率的に焼成できるといえる。 Cuソース・ドレイン電極をSAM処理してキャリア注入障壁を低減 有機TFT関連では、山形大学の研究グループがソース・ドレイン電極にコンベンショナルなAuに代わって安価なCuを用いることを提案。有機半導体とのキャリア注入障壁を低減するため、Cu電極をSAM(Self Assembled Monolayers)で表面処理した成果を報告した。

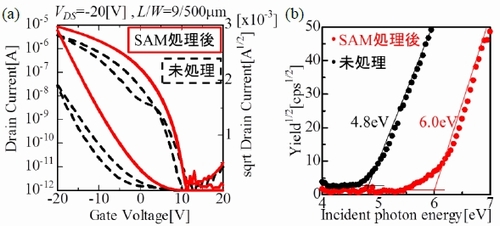

サンプルデバイスは、まずガラス基板上にゲート電極としてAl膜を膜厚30nmで真空蒸着。続いて、テフロンをスピンコートした後、150℃でベークし、膜厚220nmのゲート絶縁層を形成した。次に、Cu膜を膜厚50nmで真空蒸着し、フォトリソ+ウェットエッチング処理してチャネル長9μmのソース・ドレイン電極を形成した。この後、ペンタフルオロベンゼンチオール(PFBT)を用いてCu電極表面をSAM処理した。最後に、ペンタセン有機半導体を膜厚50nmで真空蒸着した。 図10はトランスファー特性比較で、SAMレスデバイスはヒステリシスが大きく、ON電流も低く、モビリティも0.06cm2/V・sに過ぎなかった。これに対し、SAM処理を行った場合、ON電流が増加し、ヒステリシスもほとんどみられず、モビリティ0.1cm2/V・s、ON/OFF電流レシオ105以上という高い特性が得られた。また、図10-(b)のようにSAM処理によってCu電極の仕事関数が4.8eVから6.0eVに変化したことから、ペンタセン(5.0eV)への実効的なキャリア注入注入障壁が低減された。 熱酸化膜をO2プラズマ処理してVthを制御 一方、神戸大学と東京大学の研究グループは実用デバイスへ適用するに当たって不可欠とされるVth制御法として熱酸化膜をO2プラズマ処理することを提案した。 実験では熱酸化膜(膜厚35nm、90nm、300nm、500nm)付きシリコンウェハー基板を使用。まず基板をO2プラズマ処理した後、HMDS(ヘキサメチルジシラザン)処理した。そして、膜厚45nmでペンタセン有機半導体を成膜した後、Auソース・ドレインを形成した。チャネル長は100μm、チャネル幅は1mmである。

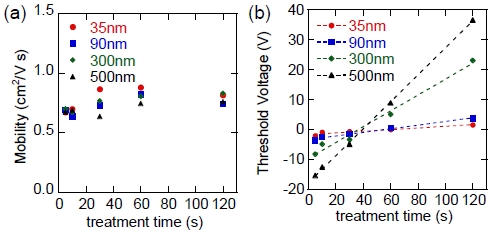

図11は飽和領域におけるキャリアモビリティとVthのO2プラズマ処理時間依存性で、モビリティはO2プラズマ処理時間にほとんど依存しない一方、VthはO2プラズマ処理時間の増加とともに正方向にシフトすることがわかる。このとき、Vthの傾きの比は熱酸化膜の膜厚比に対し一定だった。こうしたVthの変化は、O2プラズマ処理時間に比例した密度で界面近くに負の固定電荷が生じたためと考えられる。つまり、O2プラズマ処理によってモビリティを変化させずにVthが制御できるわけである。 参考文献 |

||||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |

|