|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

春季応用物理学会(3月15日〜18日) |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

3月15〜18日、早稲田大学で開かれた「2012年春季第59回応用物理学関係連合講演会」。筆者は有機エレクトロニクス、酸化物半導体、ナノカーボン分野を中心に計40件ほどの講演を聴講したが、圧倒的にインパクトがあったのがバックチャネル構造アモルファスIGZO-TFTの実現可能性を感じさせた神戸製鋼所の報告だった。Cuソース/ドレインのバリアメタルにSi/Tiを提案したもので、このテクノロジーを用いればコストポテンシャルでもIGZO-TFTがa-Si TFTを凌駕するとさえ思ったほど。この報告を含め注目講演をピックアップする。 ナノインプリント法で急峻な段差を形成し段差構造有機トランジスタに

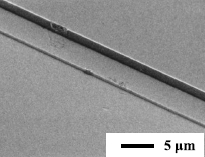

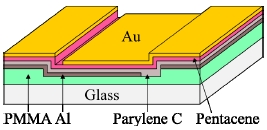

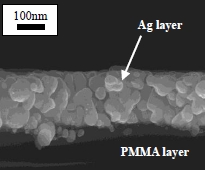

有機トランジスタ関連では、千葉大学が独自の短チャネル構造デバイスである段差型有機トランジスタ(SVC-OFET)で新たな研究成果を発表した。図1のように、SVC-OFETは段差構造を利用することでチャネル長をサブミクロン化する狙いで、従来はフォトリソ技術で段差構造を作製。今回はプロセスを簡便化するため、熱ナノインプリント法で急峻な段差構造を形成することに成功した。 まず、クロロホルムに溶解したPMMA溶液をガラス基板上にスピンコート。続いて、凸アレイパターンを設けたSi製モールドを降下させ基板を圧力4MPaで加圧し、PMMA膜をTg以上に加熱して一定時間保持。冷却後、写真1のように段差構造のあるPMMA絶縁膜を作製した。段差の深さは0.6〜1μmである。この後、ゲート電極としてAl膜を段差構造の側壁へ向かって斜め25度から真空蒸着。続いて、パリレン絶縁膜とペンタセン有機半導体膜を垂直成膜した後、Au膜をAlゲートとは逆斜め方向から蒸着してソース・ドレイン電極を形成した。段差構造断面のSEM像から求めたチャネル長は0.6μm、チャネル幅は1mmである。線形領域におけるモビリティは0.079cm2/V・s、Vthは−7.6V、OM/OFF電流レシオは105だった。 有機半導体膜にメタルプリカーサ材料をIJ印刷して自己組織化ソース/ドレインに

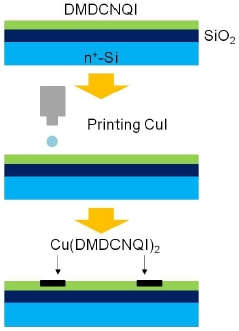

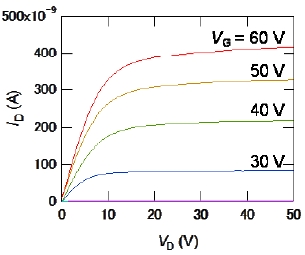

今回、有機トランジスタ関連でもっともユニークに映ったのが、東京工業大学の研究グループが発表したセルフコンタクト型有機トランジスタ。成膜した有機半導体膜を部分的に化学反応させることによって金属的電荷移動錯体にしてソース/ドレイン電極にするアイデアで、今回はインクジェットプリンティング法によって金属的電荷移動錯体ソース/ドレイン電極をセルフアラインで形成した。 まず、SiO2熱酸化膜付きシリコンウェハー基板上に、大気中でも安定で導電性も1000S/cm以上と高いn型半導体DMDCNQI(ジメチルジシアノキノンジイミン)を膜厚500nmで真空蒸着。続いて、濃度1wt%のCuIをアセトニトリル:DMSO=1:1溶液に溶解させたインクをIJ印刷し、選択的に金属的電荷移動錯体Cu(DMDCNQI)2を形成した。チャネル長は100μm、チャネル幅は1000μmである。IJ印刷回数は2〜3回で、回数が多いほど下部も金属的電荷移動錯体Cuになる。 ソース/ドレイン電極のシート抵抗値は0.2〜2.6kΩ/□、活性層との接触抵抗は235kΩ・cmで、当然のことながら活性層とソース/ドレインが連続的につながった断面が得られ、モルフォルジーの乱れもなかった。試作デバイスのモビリティは0.054cm2/V・s、Vthは25V、ON/OFF電流レシオは4×104だった。コンベンショナルなフォトリソ法やマスクスルー蒸着法で形成したAuソース/ドレインデバイスのモビリティは0.01cm2/V・sクラスであり、これに比べ5倍というハイモビリティが得られた。 いうまでもなく、この方法は用いる有機半導体材料とプリカーサ金属的電荷移動錯体材料に制約があるものの、正真正銘のセルフコンタクト型デバイスといえ、今後のさらなる研究成果にも期待がもてそうだ。

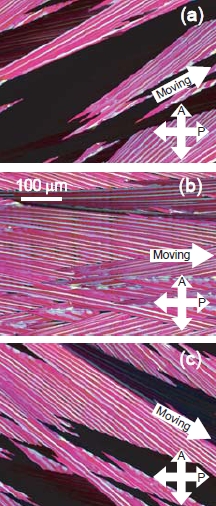

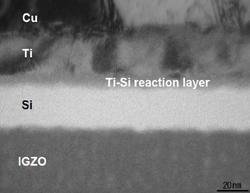

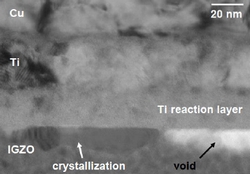

新たなウェットコート法で塗布型有機半導体を配向塗布 ここにきて有機トランジスタではウェット法による単結晶有機半導体膜が相次いで報告されるなど、有機半導体成膜法は従来の蒸着法からウェット法へ移行する動きが目立ってきている。こうしたなか、物質・材料研究機構はフロー・コーティング法と名づけたオリジナルコーティング法で高配向TIPSペンタセンを成膜したことを報告した。 フロー・コーティング法は基板の上部に可動型塗布ブレードを1.5度とわずかに上方に傾けてセットし基板と200μm程度のギャップを確保。その空隙に有機半導体溶液を注入した後、塗布ブレードを平行移動させることにより有機半導体膜を配向させながら塗布する仕組み。低沸点溶液が塗布できるほか、スピンコート法に比べ材料利用率が高く、少量の試料で実験ができるという特徴がある。 今回は濃度0.6wt%のTIPSペンタセンクロロホルム溶液を16μLを注入し、幅13㎜の塗布ブレードを200μm/sで掃引して配向TIPSペンタセン薄膜を形成した。写真2は膜の偏光顕微鏡写真で、一方向に伸びた針状結晶のアレイからなる多数のドメインで膜が構成されていることがわかる。偏光顕微鏡観察と赤外吸収スペクトルの偏光特性から、TIPSペンタセン結晶のa軸がブレードの掃引方向に沿って配向していることがわかった。 そこで、熱酸化SiO2膜付きシリコンウェハー基板上にTi(膜厚0.5nm)/Au(29.5nm)ソース・ドレイン電極を形成し、フェニルトリクロロシラン処理とペンタフルオロベンゼンチオール処理でSAM処理した後、TIPSペンタセン膜をフロー・コーティングしてボトムコンタクト型有機トランジスタを作製した。ここでチャネル長は150μm、チャンネル幅は1mmである。キャリアモビリティの異方性を調べるため、掃引方向に対してチャネル長方向が平行な素子と垂直な素子を作製したところ、どちらもヒステリシスのない良好なp型特性を示した。飽和領域におけるモビリティは前者が0.9cm2/V・s、後者が0.4cm2/V・sで、前者ではこれまでに報告されている高配向TIPSペンタセンのモビリティ(最高0.53cm2/V・s)を大きく上回ることが確認できた。また、Vthは前者が1.2V、後者が1Vで、ドレイン電流のON/OFFレシオはどちらも106以上が得られた。 ノーリスク&ハイリターン材料・エッチング技術でバックチャネル型IGZO-TFTを 今年からLCD用アクティブマトリクス素子として量産される予定のアモルファスIGZO(In-Ga-Zn-O)-TFTでは、神戸製鋼所がwonderfulと呼べるほどインパクト抜群の研究成果を発表した。研究テーマはCuソース/ドレイン向けバリアメタルの開発で、コンベンショナルなTiに代わってSi-Tiを用いることによってa-Si TFTでデファクトスタンダードとなっているバックチャネル構造を実現するという狙いだ。その研究目的はきわめて明確で、オーラル発表の質もよく、さらにその研究成果はスマッシュヒットと呼べるほどのグッドコンテンツだった。以下では、まず純粋に発表内容をレポートする。 今回の研究では、まずリファレンスとなるIGZO/Ti/Cuをスパッタリング成膜し、350℃×30分でアニールした後の断面TEM像を観察した。この結果、写真3よりTFT製造時の熱履歴によってIGZO活性層とTi層間に厚い酸化Ti層が形成されていることがわかった。また、IGZO層中にボイドや結晶相が形成されており、IGZO層が不均一化していた。これに対し、今回のIGZO/Si/Ti/Cu積層構造では写真4のようにIGZO/Si界面で酸化還元反応がほとんど見られず、明確な界面が形成されていた。もちろん、Cu層へのIGZOの拡散もない。SIMS分析でもCu中にIGZOの成分は検出されず、拡散バリア性が十分に得られることが確認できた。つまり、密着性、バリア性ともTiを完全にリプレースできるポテンシャルを備えているといえる。

エッチングによるパターニング性というさらなるアドバンテージもある。周知のように、バックチャネル構造ではIGZO活性層へのダメージ抑制のため、ソース/ドレインメタルは基本的にドライエッチングでパターニングする必要がある。いうまでもなく、Tiバリアメタルをウェットエッチングしようとすると下部のIGZOまでエッチングされてしまうなど、選択エッチング性がまったくないためである。これに対し、今回のSi/Ti積層バリアメタルでは高い選択エッチング性を利用して2段階エッチングする。具体的には、まず市販の混酸エッチャントを用いてCu膜とTi膜をウェットエッチングする。この際、下層にあるSiはほとんどエッチングされない。次に、Si膜をSF6/Ar混合ガスによってドライエッチングする。この際も下層にあるIGZOはまったくエッチングされない。そのエッチング選択性はきわめて大きく、量産プロセスでも大きすぎるほどのプロセスマージンがあるわけである。 こうした初期実験を踏まえ、6枚マスクプロセスでエッチングストッパータイプ、5枚マスクプロセスでバックチャネルタイプのIGZO-TFT(チャネル長10μm)を試作した。気になる特性だが、キャリアモビリティは前者が5.6cm2/V・s、後者が4.55cm2/V・s、Sファクターは前者が1.01V/dec、後者が0.93V/decだった。つまり、第1世代とされるエッチングストッパータイプと特性も同等だった。すなわち、従来のTi/Cuソース・ドレインにSiを挿入するだけでローコスト化で有利なバックチャネル構造デバイスが実現できるわけで、a-Si TFTの量産で一部用いられているハーフトーン露光技術を用いれば4枚マスクプロセスでIGZO-TFTが実現できると結論づけた。 以上が報告内容で、以下はこの報告を受けての筆者の考察を記したい。結論からいうと、今回の提案は“ノーリスク&ハイリターン”といっても過言ではないだろう。その費用対効果を考えると、費用は従来のTi/Cu積層にSiを挿入するだけ。いうまでもなく、Siはマテリアル的にも成膜・エッチングプロセス的にも涸れた材料であり、新たな技術開発は必要なく、その成膜・エッチングコストもたかがしれている。これに対し、効果はなんといってもバックチャネル構造が容易に実現すること。このため、コンベンショナルなエッチングストッパー構造に比べPEP数を6回から5回または4回に削減でき、もちろんSiOxをはじめとするエッチング保護膜も不要になる。気になる特性劣化も上記の報告ではみられない。従来、バックチャネル型IGZO-TFTは活性層が保護されていないためにソース/ドレイン形成工程はもちろんのこと、後工程であるパッシベーション成膜・パターニング工程でも少なからずダメージを受けるため、“当面はIGZO-TFTに適用するのは不可能”とされてきた。事実、バックチャネルIGZO-TFTの試作報告は米HPのハイブリッドプレーン型電気泳動ディスプレイ用TFT以外ではなく、この報告も詳細は不明だがsingle metallization back-channel etch processと名づけられるなど保護膜機能を使っている。つまり、純粋な意味ではバックチャネル構造とはいえないようだ。これに対し、今回の報告はこうした既成概念を一新したといってもいい。褒め言葉ではないかもしれないが、ディスプレイメーカーでもなければTFT製造プロセスのプロでもない神戸製鋼が小型サンプルとはいえバックチャネルデバイスを試作し、さらに実用的な特性が得られたのである。まさにIGZO酸化物半導体の開発者である東京工業大学 細野秀雄教授のコメント「IGZO-TFTは誰でもハイパフォーマンスのTFTが簡単に作れる」に表されるIGZO-TFTのラージアドバンテージを実証したとさえいえる。 ここでa-Si TFTとの比較も考えてみる。a-Si TFTをコンベンショナルな5枚マスクプロセスで作製する場合、3rd PEPであるソース/ドレイン・活性層一括形成工程ではTi/Al/Tiなどのソース/ドレインメタル、n+ Si活性層、a-Si接続層を一括でドライエッチングしてパターニングする。この際、最下層にあるn+ Si層はすべてをエッチング除去せずに、100nm程度という一定の厚みを残す必要があるため、あらかじめプラズマCVD成膜する際に膜厚を200nm以上と厚めにしておき、一括ドライエッチング時に途中で処理をストップする。つまり、ドライエッチング工程のプロセスマージンは決して大きくない。これに対し、Si/TiバリアメタルバックチャネルIGZO-TFTは①CuとTiをウェットエッチング、②Siをドライエッチング、と2段階エッチングが必要になるが、前記のようにエッチング選択性が大きいためプロセスマージンがきわめて大きく、製造難易度はかなり低い。この点を考慮すると、エッチング回数が増えることも相殺できるとさえいえる。つまり、原理的にはa-Si TFTとIGZO-TFTのコスト差はないと考えられる。ちなみに、4枚プロセスで作製する場合はIGZO膜をチャネル以外は完全に除去する一方、チャネル上は結果的に半分程度を削って一部を残す必要があるため、5枚プロセスのようにプロセスマージンが広くなるというアドバンテージはない。 さらに厳密に考えると、a-Si TFTとIGZO-TFTの違いはn+ Si膜とa-Si膜をプラズマCVD成膜してパターニングすることと、IGZO膜をスパッタリング成膜してパターニングするという点にしかない。すなわち、プラズマCVD成膜コストとスパッタリング成膜コストを比較するだけでいい。この場合、さまざまな見方があるだろうが、CVDガス除外システムを含めたシステムコストをトータルでみるとスパッタリングシステムの方が安くなる可能性が高い。他方、原料コストはIGZOターゲットが高価な現段階ではシラン系ガスを用いるプラズマCVDの方に分があるが、量産段階に入ってくればIGZOターゲットも安価になると予想されるため、大きな差はなくなるだろう。すなわち、トータル的にはIGZO-TFTをバックチャネル構造にすればa-Si TFTともコストで十分対抗できるわけである。もちろん、そのハイモビリティ、低温成膜性、透明性、フレキシビリティ性などを加味したクオリティではa-Si TFTを大きく凌駕するわけで、これらを考えると今回の発表はバックチャネルIGZO-TFTの実現に道を開いただけにとどまらず、IGZO-TFTを“単なる次世代アクティブ素子”だけでなく、ディスプレイ用アクティブ素子のメインマーケットで戦えるポテンシャルを示したといっても過言ではないと感じた。 Cuソース/ドレインのバリアメタルにCu合金も浮上 他方、神戸製鋼ほどのインパクトはなかったものの、アルバックもIGZO-TFTのCuソース/ドレイン用バリアメタル材料に関する研究成果を報告した。バリアメタルにはTi、Mo、そしてオリジナルのCu-Mg-Al合金を用いて、それぞれのパターニング特性やデバイス特性を比較した。 6インチシリコンウェハー基板上にまずゲート絶縁膜としてSiOx膜を膜厚215nmでプラズマCVD成膜。続いて、酸素分圧0.05PaでO2を導入してIGZO膜を膜厚50nmでスパッタリング成膜した。この後、大気雰囲気で300℃×15分間アニール処理。さらに、バリアメタル/Cuソース・ドレイン、SiOxパッシベーションを形成した。最後に、N2雰囲気において200℃または300℃で15分アニール処理した。チャネル長は10μm、チャネル幅は50μmである。

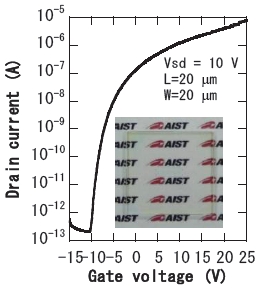

まず、バリアメタルとIGZO活性層との密着性についてはいずれのバリアメタルとも良好だった。次に非加水系エッチャントによってウェットエッチングしたところ、Cu-Mg-Al合金はきれいにエッチング除去できたのに対し、TiやMoはうまくエッチングできなかった。 IGZO膜をドライエッチングでパターニングしてバックチャネル型を 一方、産業技術総合研究所はIGZO半導体膜をドライエッチングでパターニングすることに成功。オールドライプロセスでIGZO-TFTを作製したことを報告した。周知のように、IGZO膜は酸でウェットエッチングするのが一般的で、ドライエッチングの報告はほとんどないが、ドライエッチングによってIGZO膜をパターニングすることによりバックチャネル構造を実現した。

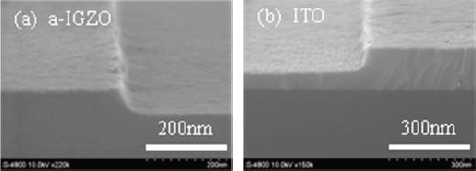

実験では、まずDCスパッタリング法によってIGZO膜を室温成膜、RFスパッタリング法によってITO膜を基板温度277℃で成膜した。成膜後、IGZO膜がアモルファス、ITO膜が多結晶であることをXRDで確認。この後、フォトリソでフォトレジストパターンを形成し、平行平板高周波印加型RIE(リアクティブイオンエッチング)装置を用いてITO膜のエッチングガスとして知られるCH4/H2混合ガスによってドライエッチングした。写真5はパワー150Wで5分間RIEを行った膜のSEM像で、IGZO膜、ITO膜とも50nm以上の段差と比較的平坦な表面が観測され、10nm/min以上のRIEが可能であることがわかった。 ここで重要なのは、同一プロセス条件ではITO膜の方がエッチングレートが高いこと。周知のようにITOソース/ドレインを用いる場合、コンベンショナルなウェットエッチング法ではIGZO層がエッチングされてしまうため、フォトレジストを塗布・パターニングした後、ITO膜をスパッタリング成膜するリフトオフ法を用いるのが一般的だ。これに対し、ドライエッチング法でITO膜をパターニングすればIGZO膜もエッチングされるが、そのエッチングレート差からプロセス条件をコントロールすれば活性層のエッチングを最小限に抑制できるわけである。 研究グループは上記の結果を受けオールドライプロセスで透明IGZO-TFTを作製。a-IGZOチャネル上に直接多結晶ITO膜を成膜した後、RIEでソース/ドレイン電極に分離することにより、図4のようにバックチャネル型透明TFTを作製することに成功した。 FIrpic青色燐光MPE素子で外部量子効率41%を達成

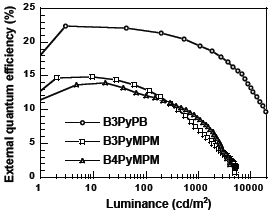

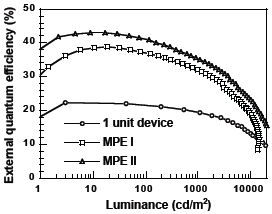

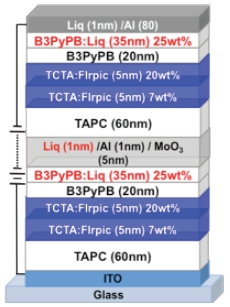

総じて有機ELに関しては目ぼしい報告が少なかったなか、山形大学は青色燐光マルチフォトンエミッション(MPE)有機ELの外部量子効率を世界最高に引き上げたことを報告した。 今回の研究に当たっては、まず研究室が独自開発した高い三重項エネルギーを持つピリジン含有電子輸送材料(B3PyPB、B3PyMPM、B4PyMPM)を用いたシングルユニット青色燐光素子を作製した。素子はITOアノード/TAPCホール輸送層(60nm)/TCTA:7wt%-FIrpic青色燐光発光層(5nm)/TCTA:20wt%-FIrpic青色燐光発光層(5nm)/電子輸送層(20nm)/Liqドープ(25wt%)電子輸送層(35nm)/Liqバッファ層(1nm)/Alカソードという構成にした。その結果、図5のように用いる電子輸送材料によって効率に大きな差がみられた。具体的には、LUMO準位が最も浅いB3PyPBを用いた場合、FIrpic素子では世界最高効率となる電力効率57lm/W、外部量子効率22%(@100cd/m2)が得られた。これに対し、深いLUMO準位のBPyMPM誘導体を用いた場合、高い三重項エネルギーを有するにも関わらず効率が半減した。 次に、図6のようにCGL(電荷発生層)ユニットにLiF or Liq/Al/MoO3/TAPCを用いたMPE素子を作製した。この際、LiFを用いた場合、MPE素子はシングルユニット素子と同程度の外部量子効率だった。他方、Liqを用いたMPE素子Ⅰは効率が大幅に向上した。これは、Liqの表面平滑性がLiFに比べ高いためと考えられる。さらに、電子輸送層にLiqをドープしたMPE素子Ⅱは効率が約2倍に向上し、外部量子効率41%が得られた。これは、Liq単膜と電子輸送層との共蒸着膜という2レイヤーにするとLiqが還元されて低電圧シフトするためと考えられる。 ちなみに、外部量子効率41%のMPE素子の電力効率は40.8lm/Wとシングルユニット素子よりも低い。いうまでもなく、これはマルチユニット化した分、駆動電圧が上昇するためである。 有機膜成膜法としてガスフロー蒸着法が急浮上 有機ELデバイスの製造プロセスでは、九州大学最先端有機光エレクトロニクス研究センターがポスト真空蒸着法としてガスフロー蒸着法を提案。成膜した膜純度と有機ELデバイス特性を報告した。

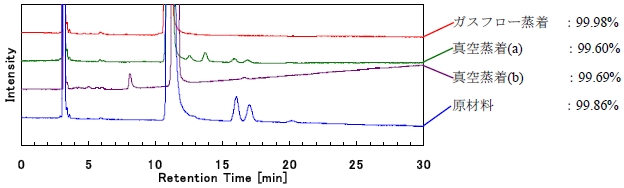

容易に想像できるように、ガスフロー蒸着法はArなどの不活性ガスをキャリアガスにして有機材料蒸気を輸送し基板上に蒸着する。キャリアガスの流量を制御することによって成膜レートなどのプロセスパラメータを高精度でコントロールできるのが特徴である。 まず、報告①8)では蒸着した膜の純度を測定するため、ガラス基板上に膜厚500nmで成膜したα-NPD膜をCH2Cl2で溶出し、その溶液を高速液体クロマトグラフィー(HPLC)で分析して膜純度と不純物比率を評価した。 表2に成膜条件、図8にHPLC分析結果のクロマトグラムと膜純度を示す。コンベンショナルな真空蒸着膜の純度が99.7%以下だったのに対し、ガスフロー蒸着膜は99.98%と極めて高い純度が得られた。また、原材料α-NPD中に含まれるメインピークより遅い保持時間のピーク成分(高沸点成分)は真空蒸着(a)、(b)膜中に含まれるが、ガスフロー蒸着膜中には含まれないことがわかった。これは、真空蒸着法は材料蒸発部・成膜環境ともに10-5Paと圧力が低いのに対し、ガスフロー蒸着法はキャリアガスを導入しているため成膜環境が10-3Pa、材料蒸発部が10Pa程度であるため高沸点成分が蒸発しにくいためと考えられる。

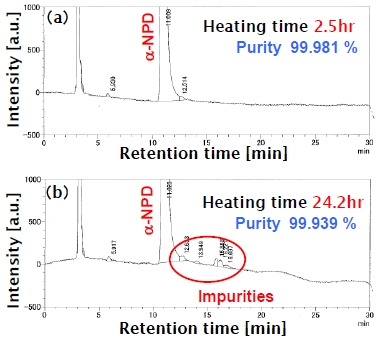

他方、報告②8)ではガスフロー蒸着装置の材料蒸発源にα-NPDを投入し、蒸発温度を290℃、キャリアガス流量を1.5sccmに固定して材料がなくなるまで蒸発させた。そして、蒸発膜(膜厚500nm)をHPLCで分析し、膜純度と不純物比率を評価した。また、ITO(150nm)/α-NPD(200nm)/Al(100nm)というホールオンリーデバイスを作製し、J-V特性と定電流駆動劣化性を評価した。 図9-(a)は蒸発開始2.5時間後、(b)は材料が枯渇する直前の24.2時間後のHPLC分析結果である。2.5時間後では99.981%ときわめて高純度なα-NPD膜が得られているのに対し、24.2時間後では高沸点成分が含まれていたため純度が99.939%に低下した。また、(b)に示されたα-NPD主成分以外の不純物成分が膜中に含まれた場合、ホールオンリーデバイスのJ-V特性は高純度膜素子に比べ駆動電圧が上昇した。これらの結果から、材料を枯渇する少し前で蒸着を終了すれば高純度膜が常時成膜できることがわかった。

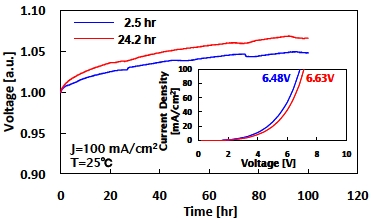

図10にホールオンリーデバイスの定電流駆動劣化における駆動電圧を示す。電流密度100mA/cm2、温度25℃、100時間の連続通電で電圧上昇を測定した。この結果、不純物成分が含まれると、高純度膜素子に比べ劣化が進行することが示唆された。 さらに、Al2O3ボートを用いた真空蒸着膜デバイス、Wボートを用いた真空蒸着膜デバイスと特性を比較したところ、ガスフロー蒸着膜デバイスでは電流密度特性が向上した。つまり、報告①で示された膜純度に比例してデバイス特性が左右されることが確認できた。くわえて、定電流駆動テストでもガスフロー蒸着膜デバイスの劣化は真空蒸着膜デバイスに比べ低く、ライフ面でも有利なことが実証できた。 ユニークな方法でAgナノワイヤーを自己整合的にネットワーク化 導電材料関連では、プリンタブルエレクトロニクスを意識してか、ナノAgに関する発表が目立った。まず、大阪大学産業科学研究所は“ポストITO”の最有力候補とされるAgナノワイヤー透明導電膜のユニークな作製方法を報告。Agナノワイヤーを自己整合的にマトリクス化して透明導電膜にする提案で、比較的シンプルな方法でITO膜を凌駕する特性が得られた。

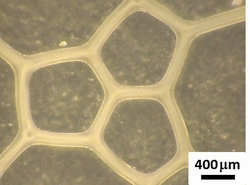

今回の実験では、まず準備としてポリオール法でAgナノワイヤーを合成。溶媒であるエチレングリコールを水に置換してAgナノワイヤー水懸濁液を作製し、さらに界面活性剤、ドデシル硫酸ナトリウム、増粘剤ラウリルジメチルアミンオキサイドを加え、ミキサーで撹拌して発泡させた。この泡立ったAgナノワイヤー水懸濁液をガラス基板に滴下し、厚さ0.3mmのスペーサを介してもう一方のガラス基板で蓋をした。この状態で室温乾燥した後、200℃で20分加熱処理した。 この結果、写真6のようにAgナノワイヤーを含む泡の稜線は多角形を連ねた網目構造を形成。Agナノワイヤーは自己組織化現象によって泡の稜線に凝集した。一方、網目構造の開口部ではAgナノワイヤーがほとんど観察できなかった。そして、泡内部の水を蒸発させると、両面ガラス基板上にAgナノワイヤーを主成分にした網目構造ネットワークが形成された。ここで泡のサイズは100〜400μm、開口サイズは0.2〜0.3㎜だった。室温乾燥後は導電性を発現しなかったが、加熱処理後はシート抵抗値320Ω/□、光透過率95%という透明導電膜が得られた。さらに、濃度を増やしたところ、光透過率は84%に低下したものの、シート抵抗値6.2Ω/□ときわめて高い導電性を発現した。いうまでもなく、これはITO膜を凌駕し、ランダムネットワークAgナノワイヤーの1/3に当たる高い値である。 ナノAg電極の密着性改善にはTgの低い密着材料を用いるのが有効 一方、山形大学有機エレクトロニクス研究センターはプリンタブルエレクトロニクスデバイスの電極材料であるナノAg電極の課題とされる下地との密着性を改善したことを報告した。

実験は、まずガラス基板上に密着層としてトルエンに溶解したPMMAを膜厚200nmでスピンコートし、120℃で1時間加熱して硬化させた。続いて、市販のAgナノインク(径10nm程度)をスピンコートし120〜160℃×1時間焼成して、膜厚300nmのAg電極を形成した。Ag膜の密着性をクロスカット法に基づいた引き剥がし試験で評価したところ、PMMAレスではまったく密着性がとれていなかったのに対し、PMMA密着層ありでは密着性が大幅に改善された。また、PMMAに代わってエポキシ樹脂とメラミンを密着層として用いたところ、前者は良好な密着性が得られたのに対し、後者では160℃以上で焼成しても密着層とAg層の界面に明確な隙間ができるなど密着性が不十分だった。これは、密着材料のTgが高いとAgの加熱処理中で十分融着せず隙間ができるためである。つまり、密着性を高めるにはPMMAのようなTgの低い材料を用いるのが好ましいといえる。なお、Ag電極自体の比抵抗はいずれも7μΩ・cm前後(@140℃焼成)と密着材料依存性がなく、電気的な特性は変わらなかった。 参考文献 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |