|

STELLA通信は㈱ステラ・コーポレーションが運営しています。 |

予講集からみる春季応用物理学会 |

|||||||||||||||||||

3月24~27日に開かれる予定だった「春季第58回応用物理学関係連合講演会」。11日に起こった東日本大震災の影響により中止となったが、応用物理学会事務局は先頃あらかじめ作製していた予稿集を発売。ここでは予稿集からトピックスを抜粋する。 高分子発光層にポリスチレンを添加して寿命を向上 まず有機ELでは、北陸先端科学技術大学院大学がF8BTにポリスチレン(PS)を混合した混合型高分子素子でライフタイムを改善したことを報告した。

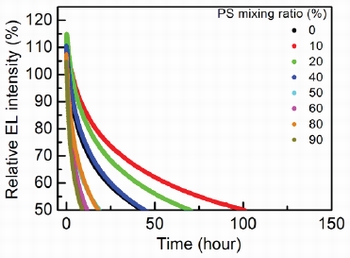

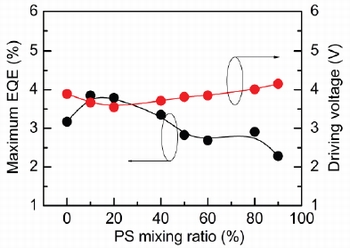

試作したのはITOアノード(膜厚50nm)/PEDOT:PSSホール注入層(60nm)/F8TFBホール輸送層(30nm)/発光層(60nm)/Baバッファ層(5nm)/Alカソード(100nm)素子で、発光層にはF8BTとPSの混合比を0~90%に変えた混合層を用いた。また、高分子層はスピンコート法、電極は真空蒸着法で成膜した。 図1に駆動電圧と外部量子効率のPS濃度依存性を示す。興味深いことにPSを添加しても駆動電圧はまったく変化せず、PSを低濃度で添加した素子ではわずかだが低下した。一方、外部量子効率はPS添加レス素子が3.14%だったのに対し、PS混合比10%素子では3.85%と1.2倍に向上した。 図2は初期輝度1000cd/m2における輝度半減寿命で、F8BTのみの素子は50時間だったのに対し、PSを10%混合すると100時間と2倍になった。他方、PSを高濃度で添加すると寿命特性は大幅に低下した。PSを低濃度で添加すると長寿命化したのは、分子間相互作用の低減によりエキシマ形成が抑制されたためと推測される。 水中レーザーアニールでPoly-Siの欠陥を不活性化 低温Poly-Si TFT関連では、奈良先端科学技術大学院大学、JST(科学技術振興機構)、高知工業高等専門学校の研究グループが水中レーザーアニール法による欠陥不活性化方法について報告した。フレキシブルディスプレイ向けとして400℃クラスが必要な既存の高温熱処理法をリプレースする狙いで、大気レーザーアニール処理に比べTFT特性も改善できるという。

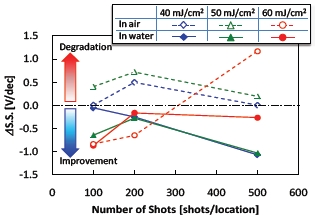

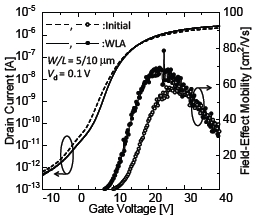

まず、エキシマレーザーアニール法で多結晶化したPoly-Si膜(膜厚50nm)を用いてトップゲート構造のnチャネルpoly-Si TFTを作製。その後、poly-Si TFTに対し水中レーザーアニールを行った。この際、レーザー照射領域においてレーザーのジュール熱によって水が蒸発し水蒸気層が形成される。この水蒸気によってPoly-Si膜中やPoly-Si膜とゲート絶縁膜の界面に存在する電気的欠陥が不活性化される。実験ではリファレンスとして大気中でもレーザーアニールも行い、TFT特性を比較した。なお、用いたのはQスイッチNd:YAGレーザー第3高調波(波長355nm)で、パルス幅約4nsec、繰り返し周波数10Hz、照射エネルギー40~60mJ/cm2でチャネル領域を中心に100×100μm領域に照射した。 図3は水中レーザーアニール前後におけるPoly-Si TFTの伝達特性で、水中レーザーアニール後、ドレイン電圧Vd=0.1VでのS値は2.41V/decから1.64V/decへ改善されるとともに、ON/OFF電流レシオも増加した。これら伝達特性の改善によってモビリティも54cm2/V・sから70cm2/V・sへ増加した。 図4に純水中あるいは大気中雰囲気でレーザーアニールを行った前後でのPoly-Si TFTのS値を示す。大気中レーザーアニールではS値はほぼすべての照射条件で劣化したのに対し、水中レーザーアニールではほぼすべての照射条件で改善された。こうした傾向はVth変化でも同様にみられた。前記のように水中レーザーアニールではレーザー照射後、水が蒸発しPoly-Si TFT基板表面が水蒸気層に曝されるため、水蒸気が欠陥不活性化に寄与したと考えられる。 重合性液晶材料をスリットコートして配向膜フリーに

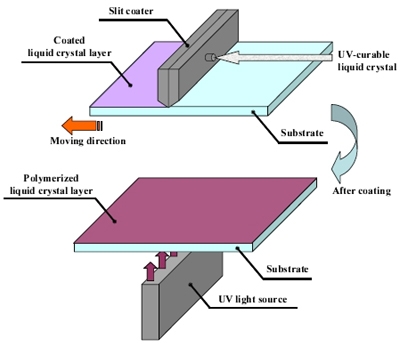

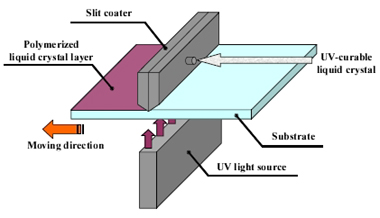

LCD関連では、長岡技術科学大学と東レエンジニアリングがスリットコート法による液晶配向法を紹介した。ポリイミド配向膜材料をレス化するアプローチで、とくに焼成が不要になるためプラスチック基板製フレキシブルLCDに有望としている。 プロセススキームは、図5のようにまず配向膜レス状態のガラス基板上に重合剤添加液晶材料をスリットコートする。この際、基板側からUV光を照射することにより重合剤が硬化し、水平配向のまま液晶層を固定される。こうして形成された配向状態は、スリットノズルからのフローによると考えられる。また、図6のように液晶材料塗布とUV照射を別々に行うと配向状態が転移し、垂直配向を示す液晶層が形成される。これらの結果、配向膜フリーで材料コストが低減できるとともに、工程数削減によるコストダウンが期待できる。ただ、現時点ではラビング配向セルほどの均一性は得られていないという。 背面露光による自己整合技術を多用して有機TFTを作製 有機トランジスタでは名古屋市工業研究所、ブラザー工業、富山大学が自己整合技術を多用したデバイスを相次いで報告した。

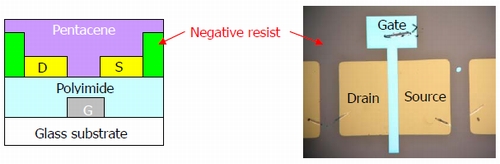

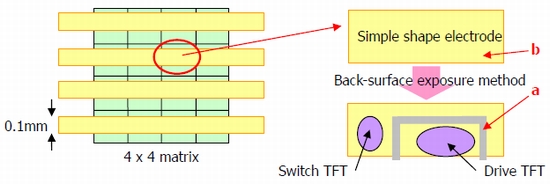

まずは背面露光技術を用いた素子分離方法で、図7のようなボトムゲート・ボトムコンタクト型素子を作製した。透明ゲート絶縁膜と不透明電極を用いる仕組みで、素子間分離にネガ型フォトレジストを使用。基板全面にスピンコートした後、ゲート、ソース、ドレインの3電極をマスクにして背面露光により自己整合パターニングした。また、ソース/ドレインの分離にもゲートをマスクにした背面露光法を用いた。つまり、2度の自己整合技術を使用するわけである。その後、有機半導体層としてペンタセン膜をベタ蒸着した。 リファレンスとして作製した素子分離レス素子はON/OFF電流レシオが50と低かったのに対し、素子分離デバイスでは2×104と大幅に向上。とくに有機TFTの集積化に有効で、7段のリングオシレータを試作し動作を確認した。 研究グループは、一つの単純形状の電極から複数の有機TFTを形成する自己整合技術も発表。とくに、ピクセル内に複数の有機TFTが必要となるアクティブマトリクス有機ELディスプレイに有効だという。

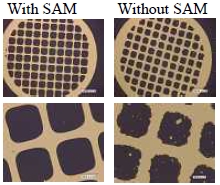

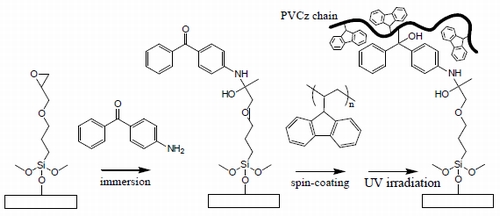

図8にそのコンセプトを示す。ポイントはゲート電極を形成する際、ゲート電極パターンと同時にaの補助パターンを形成することにある。ゲート電極パターンは、後のソース/ドレイン電極形成プロセスで背面露光法を用いる際、電極bからソースとドレインを分離するマスクとなる。一方、パターンaは電極bから二つの有機TFTを形成するための区画分け用マスクとなる。今回は電極bの形成に線幅0.1mm程度のシャドーマスクを用いて解像度100ppiのマトリクスを作製。一つのセルに含まれる二つの有機TFTの基本動作を確認した。 SAMを利用して高分子膜をパターニング 一方、東京農工大学とヒューストン大学はSAM(Self Assembled Monolayers)を用いて上層の高分子有機膜と化学結合させるとともに、UV露光~現像によってパターニングするプロセス技術を発表した。 図9にプロセスフローを示す。まずITO膜付き基板を3-glycidoxytrimethoxysilane(GPS)および4-aminobenzophenone(ABP)溶液に順次浸漬し、末端にベンゾフェノン(BP)を有するSAMを形成。次に、poly(N-vinylcarbazole)(PVCz)をスピンコートした後、UV光を約5mW/cm2で1時間照射した。続いて、物理吸着したPVCzを除去するためクロロホルム溶剤で洗浄し、洗浄前後の膜厚と対水接触角を測定した。最後に、フォトマスクを介したUV露光~現像によってPVCz膜をパターニングした。

BP末端はUV照射によってラジカルを形成し、PVCz鎖のC-H部位と結合すると考えられる。BPのSAMを形成した時点で膜厚は4.5nm、接触角は66度だった。この表面にPVCz膜を膜厚100nmでスピンコートすると、接触角は85度に増大した。その後、クロロホルムで洗浄すると、SAM膜なしおよびUV照射なしでは膜厚が約5nmに減少するとともに、接触角は65度に低下した。これらの結果から、SAM膜レスあるいはUV照射レスの場合、スピンコート膜は溶媒で完全に除去されたと考えられる。これに対し、PVCz膜をSAM膜上に塗布してUV照射すると、クロロホルム洗浄しても膜厚と接触角はほとんど変化しなかった。この結果、基板に強固に結合したPVCz膜が形成されたと考えられる。 写真10にUV露光~現像によるPVCzパターニング例を示す。SAM膜の有無に関わらず、PVCzはUV照射によって不溶化してパターンを形成するが、SAM膜表面では密着性の高い薄膜が形成されるため明瞭なパターンが形成されたのに対し、SAM膜のない表面ではパターンが剥離した。以上の結果から、末端にBPを持つSAMを利用することにより、基板表面に強固な化学結合を持つ高分子薄膜が形成できるとともに、露光~現像によってパターニングできることが確認できた。 低電圧駆動のp型有機発光トランジスタが

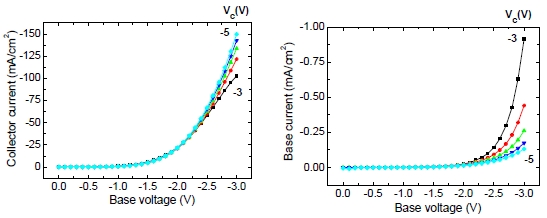

他方、山形大学は独自の縦型メタルベース有機トランジスタ(MBOT)で新たな研究成果を報告した。周知のように、MBOTではベース電極をキャリアが透過する必要があり、従来、こうした電流透過が観測されるのはペリレンビスイミドやC60というn型有機半導体材料に限られていた。今回は最も標準的なp型材料であるペンタセンとCuPcを組み合せることにより、p型で電流増幅を実現するとともに駆動電圧を低減した。 ITOアノード付き基板上にCuPc(膜厚400nm)とAl(10nm)を真空蒸着し大気下で150℃×1時間熱処理した後、ペンタセン(100nm)とAu(30nm)を蒸着して素子を作製した。そして、ITOをコレクター電極、Alをベース電極、Auをエミッタ電極としてエミッタ接地における電流変調特性を測定した。 図10に電流変調特性(出力特性と入力特性)を示す。ペンタセンのみの素子に比べ大幅に低電圧化し、VC=-5V、VB=-3Vの時に約150mA/cm2のコレクタ電流が観測された。また、電流増幅率(hFE)は1000を超え、ON/OFF電流レシオはは722に達した。これは最適化されたn型MBOTに近い値である。 高耐圧のIGZO-TFTでFEDを制御 ここにきてTFT-LCDのアクティブマトリクス素子として量産採用が決まったIGZO(In-Ga-Zn-O)関連では、産業技術総合研究所がTFT以外の新たな応用可能性を示した。

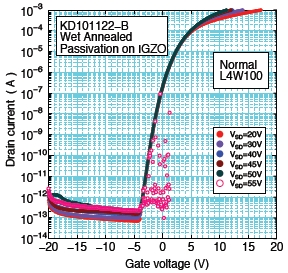

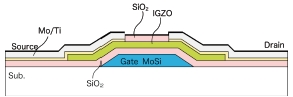

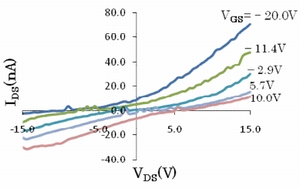

研究グループはこれまで低温Poly-Si TFT一体型FEA(Field Emitter Array)による超高輝度FEDを試作してきたが、FEAの駆動電圧が50V程度と高いため、低温Poly-Si TFTはLDD構造やマルチゲート構造を選択せざるを得なかった。しかし、その高い耐圧特性を得るにはTFTサイズを100μm以上にする必要があり、FEDを高精細化するのが難しかった。そこで、バンドギャップが3eV程度と広いため高耐圧素子がスモールサイズで実現できるIZGO-TFTでFEAを制御することにした。 実験では、IGZO活性層をDCスパッタリング成膜したボトムゲート型TFTを試作した。チャネル長は4μm、チャネル幅は100μmである。IGZO-TFT完成後、水蒸気添加した酸素雰囲気中で400℃×1時間アニール処理した。 図12は試作TFTに対しソースドレイン電圧(Vsd)を20Vから5Vずつ上げていったときのVg-Id特性である。Vsdが50Vまではほぼ同様の特性を示し、Vsd=55Vで破壊が起こった。しかし、これはソース~ドレイン間での破壊ではなく、ゲートとドレイン間の絶縁膜の破壊だった。この結果から少なくともソース・ドレイン耐圧は50V以上であることが確認できた。また、Vsd=50Vの状態でもOFF電流がpA以下と小さいため、エミッタから放出される電流をほぼ完全に遮断できると考えられる。 CNTを紙の原料にしてペーパートランジスタを

CNT(カーボンナノチューブ)では、横浜国立大学がCNTを紙の原料に用いたペーパートランジスタというユニークなニューデバイスを報告した。 まず、市販の半導体性CNT溶液(純度90%、密度1mg/100ml)を用いて複合紙を作製する。具体的には、①パルプ100mgを水10mLに分散させ型(2.5×2.5cm)に流し込んで紙を作製する、②半導体性CNT溶液40mLを作製した紙の上から滴下し乾燥させる、③絶縁体として①と同様に紙を作製し、和紙作製プロセスで用いられている梳き合わせ技術により半導体CNT複合紙との層構造をつくる、④ゲート・ソース・ドレイン電極としてAuを膜厚50nmでスパッタリング成膜してMISFETを作製する、といった仕組み。作製したサンプルの厚さは0.6mm程度である。 図13はVDS-IDS特性で、VGSに逆バイアス電圧を印加するにしたがってペーパートランジスタの電流値が変化していることがわかる。つまり、pMOSとしての性質を示している。周知のように、CNTをトランジスタのチャネルに使用するとp型特性を示す。以上からソース・ドレイン電極間にチャネルが形成されている可能性があるとしている。 UV硬化樹脂を用いた転写法で大面積基板にグラフェン薄膜を “古くて新しいナノマテリアル”であるグラフェンについては、ソニーが透明導電膜として大面積基板にも対応できる転写プロセスを報告した。 プロセスフローは、まず銅箔上にグラフェン薄膜を熱CVD法で成膜。次に、グラフェン薄膜上に溶媒フリーのUV硬化性樹脂を塗布した後、ガラス基板と貼り合わせる。続いて、UV光を照射して樹脂を硬化させ、硝酸鉄水溶液によって銅箔をエッチング除去する。この結果、樹脂に支持されたグラフェン薄膜が得られる。なお、溶媒を含むPVPと架橋剤の混合溶液を用いて転写したリファレンスサンプルも作製した。

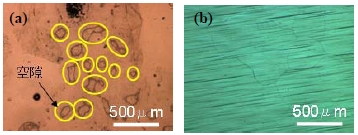

写真2にグラフェン/樹脂/ガラス構造の光学顕微鏡写真を示す。PVPを樹脂層に用いた場合、貼り合わせ後に溶媒が揮発するため気泡が空隙として残るが、UV硬化性樹脂では溶媒が存在しないため、そうした空隙が発生せず、全面に均一なグラフェン薄膜が転写できた。また、グラフェン薄膜のシート抵抗値もPVPを用いた場合は890±170Ω/□、UV硬化性樹脂を用いた場合は450±11Ω/□と後者の方が低く、導電性でも優位性があることがわかった。 参考文献 |

|||||||||||||||||||

| REMARK 1)Stella通信はFPD&PCB関連ニュースの無償提供コーナーです(ステラ・コーポレーションがFPDやPCBそのものを製品化しているわけではありません)。 2)この記事はステラ・コーポレーション 電子メディア部が取材して記事化したものです。 |