|

STELLA捠怣偼噴僗僥儔丒僐乕億儗乕僔儑儞偑塣塩偟偰偄傑偡丅 |

IDW'10乣桳婡ELD曇 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

丂桳婡ELD偱偼丄搶幣偲嬨廈戝妛偺尋媶僌儖乕僾偑敪昞偟偨惵怓椨岝慺巕偑嵟戝偺僀儞僷僋僩傪梌偊偨丅偦偺奜晹検巕岠棪偼幚偵20.9亾偲棟榑尷奅偵嬤偄儗儀儖偱丄偟偐傕僂僃僢僩僾儘僙僗偱惉枌偟偨揰傕摿昅偵抣偡傞丅

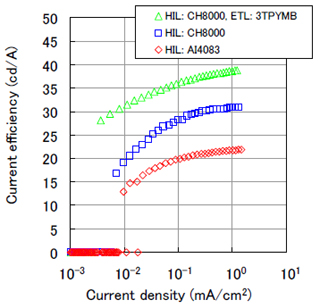

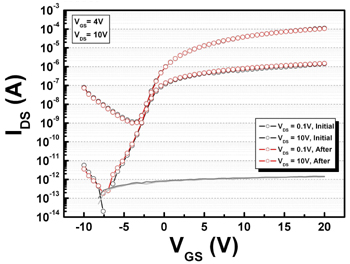

丂婎杮揑側僨僶僀僗峔惉偼ITO傾僲乕僪/PEDOT:PSS儂乕儖拲擖憌/惵怓椨岝敪岝憌/CsF揹巕拲擖憌/Al僇僜乕僪偱丄儂乕儖拲擖憌偲敪岝憌偼僗僺儞僐乕僩朄丄揹巕拲擖憌偲僇僜乕僪偼恀嬻忲拝朄偱惉枌偟偨丅敪岝嵽椏偼儂僗僩偵PVK(60wt亾)丄揹巕桝憲傾僔僗僩偵OXD-730(30wt亾)丄僪乕僷儞僩(10wt亾)偵FIrpic偲Fir6傪巊梡丅偙傟傜傪僋儘儘儀儞僛儞梟攠偵梟夝偝偣偨屻丄僔儕僐儞僂僃僴乕忋偵僗僺儞僐乕僩偟N2娐嫬偱80亷亊30暘姡憞偝偣偨丅側偍丄偡傋偰偺嵽椏偲傕巗斕昳傪巊梡偟偨丅 丂廃抦偺傛偆偵丄椨岝僷僱儖偺岠棪傪崅傔傞偵偼僪乕僷儞僩撪偱嶰廳崁椼婲巕傪岠棪傛偔暵偠崬傔傞昁梫偑偁傞丅偙傟偵偼丄儂僗僩偺嶰廳崁僄僱儖僊乕傪僪乕僷儞僩偺嶰廳崁僄僱儖僊乕傛傝傕崅偔偟側偗傟偽側傜側偄丅偙偺偨傔丄傑偢PVK偺嶰廳崁僄僱儖僊乕傪應掕偟偨偲偙傠2.72eV偲尒愊傕傜傟丄FIrpic(2.65eV)傛傝傕崅偄偙偲偑妋擣偱偒偨丅恾1偼PVK儂僗僩偵惵怓椨岝僪乕僷儞僩傪5wt亾僪乕僾偟偨嵺偺椨岝尭悐嬋慄偱丄椨岝敪岝偼帪娫偵斾椺偟偰儕僯傾偵尭悐偡傞丅偙傟偼丄僪乕僷儞僩偐傜儂僗僩傊偺嶰廳崁僄僱儖僊乕偺堏摦偑傎偲傫偳側偔丄儂僗僩偺嶰廳崁僄僱儖僊乕偑僪乕僷儞僩偺嶰廳崁僄僱儖僊乕傛傝傕崅偄偙偲偐傜僪乕僷儞僩撪偵暵偠崬傔傜傟傞偨傔偱偁傞丅 丂嶰廳崁椼婲巕偺暵偠崬傔偵偼僉儍儕傾桝憲憌偺慖戰傕廳梫偱偁傞丅偙偺偨傔丄慜婰偺傛偆偵揹巕桝憲嵽椏偲偟偰嶰廳崁僄僱儖僊乕2.7eV偺OXD-7傪敪岝憌偵僪乕僾偟偨丅傑偨丄PEDOT/PSS偵偼椼婲巕偺僽儘僢僉儞僌摿惈偑偁傝丄偦偺岠壥傪専徹偡傞偨傔丄PEDOT偲PSS偺斾棪1:6偺乽AI4083乿偲1:20偺乽CH8000乿傪梡偄偰偦傟偧傟偺僒儞僾儖僨僶僀僗傪斾妑偟偨丅恾2偵儂乕儖拲擖嵽椏偺堘偄偵傛傞僨僶僀僗摿惈斾妑傪帵偡丅PSS儕僢僠側CH8000僨僶僀僗偺揹棳岠棪偼AI4083僨僶僀僗偵斾傋崅偔側偭偨丅偙傟偼丄儂乕儖拲擖憌偲敪岝憌偺奅柺偑PSS儕僢僠忬懺偵側偭偰偍傝丄敪岝憌撪偵偍偗傞椼婲巕暵偠崬傔偑廫暘側偨傔偲峫偊傜傟傞丅

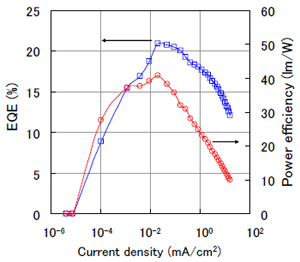

丂椼婲巕暵偠崬傔岠壥傪偝傜偵崅傔傞偨傔丄嶰廳崁僄僱儖僊乕偑2.98eV偲崅偄3TPYMB傪揹巕桝憲憌偲偟偰憓擖偡傞偙偲偵偟偨丅幚嵺丄恾2偐傜傕3TPYMB揹巕桝憲憌傪愝偗傞偲岠棪偑岦忋偡傞偙偲偑傢偐傞丅偄偆傑偱傕側偔丄偙傟傜偺寢壥偼嶰廳崁椼婲巕暵偠崬傔岠壥偑岦忋偟偨偨傔偱偁傞丅 丂恾3偼FIrpic僪乕僷儞僩偺僪乕僾棪傪1乣10wt亾偲曄摦偝偣偨嵺偺揹棳岠棪偱丄FIrpic傪3乣5wt亾僪乕僾偡傞偲岠棪偑崅偔側傞偙偲偑傢偐傞丅偙傟偵懳偟丄僪乕僾棪偺憹壛偵偲傕側偭偰岠棪偑掅壓偡傞偺偼丄FIrpic暘巕娫偱僋僄儞僠儞僌偑惗偠傞偨傔偲峫偊傜傟傞丅 丂忋婰偺幚尡偐傜慺巕峔惉傪ITO(100nm)/PEDOT:PSS(CH8000丄45nm)/椨岝敪岝憌(PVK:67wt亾丄OXD-7:30wt亾丄FIrpic:3wt%丄70nm)/3TPYMB(25nm)/CsF(1nm)/Al(150nm)偵曄峏偟偨丅恾4偼揹棳枾搙偲岠棪偺娭學偱丄奜晹検巕岠棪20.9亾丄揹椡岠棪40lm/W偲偄偆崅岠棪偑摼傜傟偨丅偙傟偼丄揾晍宆僨僶僀僗偱偼悽奅嵟崅偵摉偨傞丅 丂偝傜偵丄Ir(flpy)2(acac)墿怓椨岝僪乕僷儞僩傪FIrpic偲偲傕偵僪乕僾偟偨敀怓僨僶僀僗傪嶌惢偟偨偲偙傠丄奜晹検巕岠棪19.8亾丄揹椡岠棪52lm/W丄CIE怓搙x亖0.32丄y亖0.45偲僴僀僷乕僼僅儞儅儞僗偑摼傜傟偨丅 掅暘巕仌崅暘巕僴僀僽儕僢僪僷僱儖偱惵怓敪岝摿惈傪夵慞 丂僜僯乕偼丄掅暘巕儗僀儎乕偲崅暘巕儗僀儎乕傪僴僀僽儕僢僪壔偟偨怴偨側僷僱儖峔憿乽Super Hybrid OLED乿偵偮偄偰敪昞偟偨丅

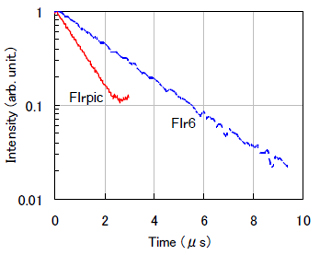

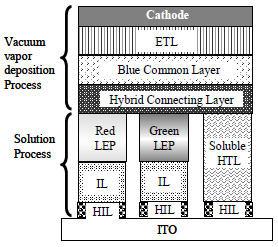

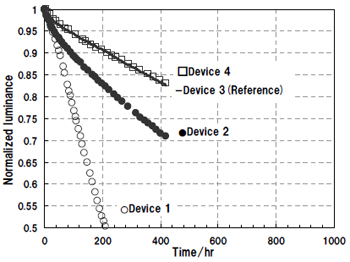

丂恾5偵偦偺峔憿傪帵偡丅儂乕儖拲擖憌丄僀儞僞乕儗僀儎乕丄惵怓埲奜偺敪岝憌丄揾晍宆揹巕桝憲憌偼僉僔儗儞梟攠儀乕僗偺揾晍塼傪僗僺儞僐乕僩丅偦偺懠偼僐儞儀儞僔儑僫儖側恀嬻忲拝朄偱惉枌偟偨丅 丂揾晍宆儂乕儖桝憲嵽椏偼丄僐儞儀儞僔儑僫儖側僀儞僞乕儗僀儎乕嵽椏偲偟偰梡偄傜傟傞TFB偲丄HOMO儗儀儖偑崅偔惵怓嫟捠敪岝憌偵揔偟偨掅暘巕嵽椏(HTL-1)傪専摙丅偦偺摿惈傪専徹偡傞偨傔丄嘆僨僶僀僗1丗ITO/儂乕儖拲擖憌/僗僺儞僐乕僩TFB儂乕儖桝憲憌/惵怓嫟捠敪岝憌(BCL)/ETL-1揹巕桝憲憌/揹巕拲擖憌/Al丄嘇僨僶僀僗2丗ITO/儂乕儖拲擖憌/僗僺儞僐乕僩HTL-1儂乕儖桝憲憌/BCL/ETL-1揹巕桝憲憌/揹巕拲擖憌/Al丄嘊僨僶僀僗3丗ITO/儂乕儖拲擖憌/忲拝HTL-1儂乕儖桝憲憌/BCL/ETL-1揹巕桝憲憌/揹巕拲擖憌/Al丄偲偄偆3庬椶偺僴僀僽儕僢僪惵怓僨僶僀僗傪嶌惢偟偨丅昞1偵揹棳枾搙10mA/cm2帪偵偍偗傞摿惈斾妑傪帵偡丅偄偢傟偺僨僶僀僗偲傕怓搙偼x亖0.14丄y亖0.09偩偭偨偑丄僨僶僀僗2偼僨僶僀僗1傛傝傕岠棪偑崅偐偭偨丅偮傑傝丄僴僀僽儕僢僪僨僶僀僗偱偼儂乕儖桝憲嵽椏偺慖掕偑傛傝廳梫偱偁傞偙偲偑傢偐偭偨丅 丂恾6偵儔僀僼僞僀儉偺斾妑傪帵偡丅僨僶僀僗2偺庻柦偼僨僶僀僗1偵斾傋挿偐偭偨偑丄儕僼傽儗儞僗偱偁傞僨僶僀僗3偵偼媦偽側偐偭偨丅偙傟偼丄僗僺儞僐乕僩僾儘僙僗拞偵HTL-1枌昞柺偵僐儞僞儈僱乕僔儑儞偑敪惗偟偨偨傔偲峫偊傜傟傞丅偦偙偱丄HTL-1儂乕儖桝憲憌偲BCL娫偵恀嬻忲拝朄偵傛傝僴僀僽儕僢僪嫟捠儗僀儎乕(HCL)傪憓擖偡傞偙偲偵偟偨丅偙傟偑僨僶僀僗4(ITO/儂乕儖拲擖憌/僗僺儞僐乕僩HTL-1儂乕儖桝憲憌/HCL/BCL/ETL-1揹巕桝憲憌/揹巕拲擖憌/Al)偱丄昞1偺傛偆偵岠棪偑6.1cd/A偵傾僢僾偟偨丅偝傜偵丄庻柦傕僨僶僀僗2偵斾傋岦忋偟丄僨僶僀僗3偲傎傏摨摍偑摼傜傟偨丅

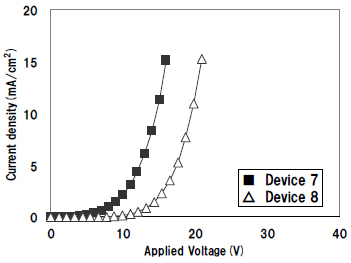

丂惵怓僨僶僀僗偵懕偒丄愒怓偲椢怓偺Super Hybrid Device傕嶌惢丅峔憿偼僨僶僀僗5偱丄儕僼傽儗儞僗偲偟偰ITO/儂乕儖拲擖憌/僀儞僞乕儗僀儎乕/崅暘巕敪岝憌/揹巕拲擖憌/Al偲偄偆僆乕儖崅暘巕僨僶僀僗(僨僶僀僗6)傕嶌惢偟偨丅昞2偼揹棳枾搙10mA/cm2帪偵偍偗傞摿惈斾妑偱丄僀僯僔儍儖摿惈偼傎傏摨偠偩偭偨丅傑偨丄庻柦傕傎傏摨摍偩偭偨丅偝傜偵丄揹棳枾搙傪0.1乣10mA/cm2偲曄壔偝偣偰敪岝偝偣偰傕愒怓僨僶僀僗丄椢怓僨僶僀僗偲傕怓搙偼傎偲傫偳曄壔偟側偐偭偨丅偙傟傜偺寢壥偼丄愒怓僨僶僀僗丄椢怓僨僶僀僗偲傕揔愗側桳婡憌側傜偽敪岝憌乣僇僜乕僪娫偵憓擖偟偰傕儀乕僗摿惈偑楎壔偟側偄偙偲傪堄枴偡傞丅 丂尋媶僌儖乕僾偼僐儞儀儞僔儑僫儖側僴僀僽儕僢僪僨僶僀僗偱偼HCL傗BCL傪憓擖偡傞偲偙傟傜偺儗僀儎乕撪偱僉儍儕傾偺嵞寢崌偑堦晹婲偙傝丄敪岝怓偑曄壔偡傞偲峫偊偰偄偨偑丄惵怓僨僶僀僗5偱偼偦偆偟偨尰徾偑娤嶡偝傟側偐偭偨丅偙傟傜偺僨僶僀僗偵偍偗傞僉儍儕傾桝憲惈偺堘偄傪専徹偡傞偨傔丄僆乕儖僂僃僢僩僾儘僙僗偱儂乕儖僆儞儕乕僨僶僀僗(僨僶僀僗7丗ITO/儂乕儖拲擖憌/僀儞僞乕儗僀儎乕/崅暘巕敪岝憌/AuGe)丄僆乕儖忲拝僾儘僙僗偱儂乕儖僆儞儕乕僨僶僀僗(僨僶僀僗8丗ITO/儂乕儖拲擖憌/僀儞僞乕儗僀儎乕/崅暘巕敪岝憌/HCL/BCL/揹巕桝憲憌/AuGe)傪嶌惢偟偨丅恾7偼J-V摿惈偱丄僨僶僀僗8偼僨僶僀僗7偵斾傋嬱摦揹埑偑忋徃偟偨丅偙傟偼丄儂乕儖偺拲擖偑忲拝憌偵傛偭偰傛傝岠壥揑偵僽儘僢僋偝傟傞偨傔偲峫偊傜傟傞丅

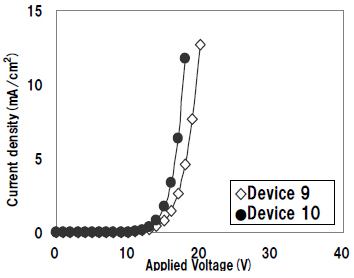

丂摨條偵丄揹巕僆儞儕乕僨僶僀僗傕僂僃僢僩僾儘僙僗僨僶僀僗(僨僶僀僗9丗Al/儂乕儖拲擖憌/僀儞僞乕儗僀儎乕/崅暘巕敪岝憌/揹巕拲擖憌/Al)偲忲拝僨僶僀僗(僨僶僀僗10丗Al/儂乕儖拲擖憌/僀儞僞乕儗僀儎乕/崅暘巕敪岝憌/HCL/BCL/揹巕桝憲憌/揹巕拲擖憌/Al)傪嶌惢偟偨丅恾8偼J-V摿惈偱丄僨僶僀僗9偼僨僶僀僗10偵斾傋揹埑偑忋徃偟偨丅偙傟偼丄僨僶僀僗10偼HCL/BCL/ETL-1偵傛偭偰揹巕偑傛傝拲擖偟傗偡偔側偭偨偨傔偲峫偊傜傟傞丅偮傑傝丄揹巕儌價儕僥傿偺娤揰偱偼ETL-1偺崅偄揹巕桝憲惈偵傛偭偰惵怓敪岝嫮搙偑崅傑傞偨傔偱偁傞丅 丂忋婰偐傜Super Hybrid devices偼愒怓敪岝丄椢怓敪岝偺僼傽儞僟儊儞僞儖僘摿惈傪堐帩偟側偑傜惵怓敪岝偺摿惈傪岦忋偝偣傞偙偲偑偱偒傞偲寢榑偯偗偨丅 僼儗僉僔僽儖僷僱儖岦偗偵掅壏峝壔CF傪巊梡

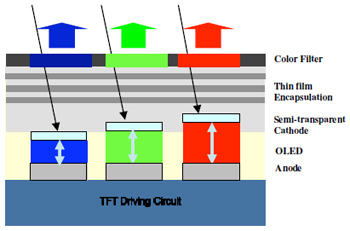

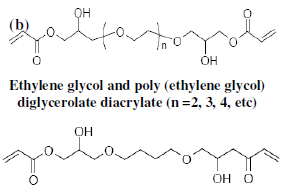

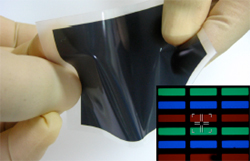

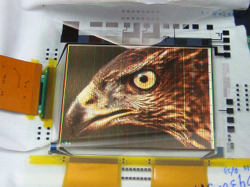

丂偄傑傗惢昳壔傕帪娫偺栤戣偲側偭偰偄傞僼儗僉僔僽儖桳婡ELD偵偮偄偰偼丄Samsung Advanced Institute of Technology丄Samsung Mobile Display丄Seoul National University偑掅壏CF嶌惢僾儘僙僗偲枌晻巭媄弍傪梡偄偨僼儖僇儔乕僷僱儖傪曬崘偟偨丅掅壏宍惉CF埲奜丄偲偔偵栚怴偨偟偄敪昞偱偼側偐偭偨偑丄Samsung Mobile Display偼偙偺媄弍傪梡偄偰僔乕儉儗僗側5.4宆僼僅儖僟僽儖僷僱儖/儀儞僟僽儖僷僱儖(幨恀1)傪帋嶌丅儅乕働僢僩偵搊応偡傞擔傕嬤偄偨傔丄姼偊偰庢傝忋偘傞偙偲偵偟偨丅 丂恾9偵帋嶌偟偨僩僢僾僄儈僢僔儑儞宆僷僱儖偺峔憿傪帵偡丅0.55噊岤僈儔僗婎斅忋偵僪儔僀價儞僌TFT偲僗僀僢僠儞僌TFT傪愝偗偨掅壏Poly-Si TFT傪嶌惢偟偨屻丄桳婡EL憌傪宍惉偟偨丅桳婡EL偼Ag/ITO傾僲乕僪乣儂乕儖拲擖憌乣儂乕儖桝憲憌乣RGB敪岝憌乣揹巕桝憲憌乣Mg:Ag敿摟夁惈僇僜乕僪偲堦斒揑側峔惉偱丄儅僀僋儘僉儍價僥傿岠壥傪帩偨偣傞偨傔丄儂乕儖桝憲憌偺枌岤傪R偑175nm丄G偑120nm丄B偑60nm偲僒僽僺僋僙儖枅偵曄峏偟偨丅桳婡EL宍惉屻偼Al2O3柍婡巁壔枌偲億儕傾僋儕儖巁桳婡憌傪岎屳偵儅儖僠儗僀儎乕偱僗僞僢僋偟偰晻巭丅嵟屻偵丄僽儔僢僋儅僩儕僋僗晅偒偺CF傪宍惉偟偨丅

丂廃抦偺傛偆偵丄僐儞儀儞僔儑僫儖側桳婡ELD偼慜柺偵曃岝僼傿儖儉傪揬偭偰僐儞僩儔僗僩傪崅傔傞偑丄僼儗僉僔僽儖僷僱儖偱偼攋傟傗偡偄偨傔巊梡偡傞偺偑擄偟偄丅偦偙偱丄儅僀僋儘僉儍價僥傿RGB撈棫敪岝亄CF偲偄偆峔惉偵偟偨丅偙偺寢壥丄曃岝僼傿儖儉儗僗偱傕奜岝斀幩偑梷惂偝傟偰崅僐儞僩儔僗僩傪妋曐偱偒偨丅 丂偲偙傠偱丄堦斒揑側僇儔乕儗僕僗僩偼彮側偔偲傕200亷偱峝壔偝偣傞昁梫偑偁傞丅偟偐偟丄偙偺壏搙偱偼宍惉嵪傒偺桳婡EL憌傊偺僟儊乕僕偑寽擮偝傟傞傎偐丄僾儔僗僠僢僋僼傿儖儉傪僒僽僗僩儗乕僩偵巊梡偡傞偙偲偑擄偟偔側傞丅偦偙偱丄UV徠幩亄掅壏張棟(90亷)偱壦嫶偡傞僕傾僋儕儗乕僩宯僇儔乕儗僕僗僩(撈BASF惢)傪梡偄偨丅恾10偼偦偺暘巕峔憿偱丄峝壔壏搙50亷偱80亾偲崅偄壦嫶惈偑摼傜傟傞丅傑偨丄偙偺嵽椏偼暘嶶埨掕惈丄梟夝惈丄働儈僇儖埨掕惈偵傕桪傟傞丅幨恀2偼億儕僀儈僪僼傿儖儉忋偵偙偺僇儔乕儗僕僗僩傪僷僞乕僯儞僌偟偨僼儗僉僔僽儖CF偱丄嬋棪敿宎1噊偲偄偆僼儗僉僔僽儖惈偑摼傜傟偨丅 悽奅嵟彫偺5枃儅僗僋偱掅壏Poly-Si TFT傪嶌惢

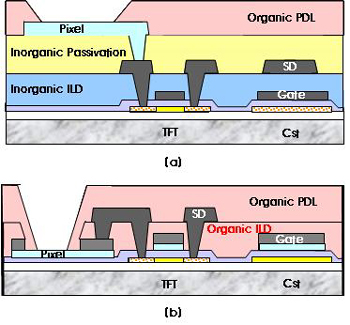

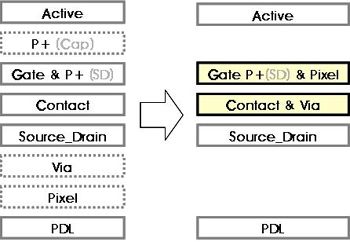

丂惢憿僾儘僙僗娭楢偱偼丄Samsung Mobile Display偑5枃僼僅僩儅僗僋偱桳婡ELD梡掅壏Poly-Si TFT傪嶌惢偡傞偙偲偵惉岟偟偨丅傕偪傠傫丄5枃儅僗僋偼LCD岦偗傪壛偊偰傕悽奅嵟彮偺儅僗僋枃悢偱偁傞丅 丂帋嶌偟偨偺偼儃僩儉僄儈僢僔儑儞峔憿偺12宆儚僀僪XGA僷僱儖丅恾11偵8枃儅僗僋僾儘僙僗傪梡偄偨僐儞儀儞僔儑僫儖側僷僱儖偲崱夞偺5枃儅僗僋僷僱儖偺峔憿傪帵偡丅5枃儅僗僋僾儘僙僗偼僎乕僩偲傾僲乕僪夋慺揹嬌傪僗僞僢僉儞僌偟偰堦妵僷僞乕僯儞僌偟偨偺偑摿挜偱丄偙偺寢壥丄恾12偺傛偆偵夋慺揹嬌偲僐儞僞僋僩儂乕儖偺僷僞乕僯儞僌岺掱傪僗僉僢僾偡傞偙偲偑偱偒傞丅傾僲乕僪夋慺揹嬌偼僨乕僞儔僀儞僷僞乕僯儞僌屻偵奐岥偡傞丅傑偨丄戝宆僷僱儖偵懳墳偡傞偨傔丄a-Si傪Poly-Si壔偡傞嵺偺RTA(Rapid Thermal Annealing)僾儘僙僗傪儗僗壔偟偨丅側偍丄偳偺傛偆偵Poly-Si壔偟偨偺偐偵偮偄偰偼怗傟偰偄側偄丅 丂偦偺TFT摿惈傪昡壙偟偨偲偙傠丄僉儍儕傾儌價儕僥傿偼廬棃偺RTA僾儘僙僗僨僶僀僗偑97cm2/Vec偩偭偨偺偵懳偟丄崱夞偺RTA僾儘僙僗儗僗僨僶僀僗偼67cm2/Vec偲掅偐偭偨丅傑偨丄廬棃偺柍婡SiNx僀儞僞乕儗僀儎乕TFT偲崱夞偺僆乕僈僯僢僋僀儞僞乕儗僀儎乕TFT傪斾妑偡傞偲丄屻幰偺儌價儕僥傿偼59cm2/Vec偲慜幰偵斾傋掅壓偟偨丅昞3偵RTA僾儘僙僗偺桳柍偵傛傞摿惈偺堘偄傪帵偡丅

丂忋婰偺TFT摿惈傪夵慞偡傞偨傔丄僎乕僩愨墢枌傪掅壏張棟偡傞僾儘僙僗傪峫埬偟偨丅崅壏惉枌僎乕僩愨墢枌TFT偲掅壏惉枌僎乕僩愨墢枌TFT傪嶌惢丅屻幰偼儌價儕僥傿偑曄摦偣偢S僼傽僋僞乕偑0.38V/dec偐傜0.3V/dec偵掅壓偟偨丅偦偙偱丄僎乕僩愨墢枌峔憿傪SiNx/SiO2(NO)偐傜SiO2/SiNx/SiO2(ONO)偵曄峏偟偨丅偦偺寢壥丄NO僨僶僀僗偼儌價儕僥傿偑72cm2/Vec偩偭偨偺偵懳偟丄ONO僨僶僀僗偼儌價儕僥傿偑81cm2/Vec偵憹壛偟偨丅

丂偲偙傠偱丄僷僱儖偺岝庢傝弌偟岠棪傪崅傔傞偵偼夋慺揹嬌偺捈壓偵偁傞儗僀儎乕偼夋慺揹嬌嵽椏偲偺孅愜棪嵎偑戝偒偄昁梫偑偁傞丅偦偺孅愜棪偼SiO2偑1.47丄SiNx偑1.93(630nm帪)偱偁傞丅堦曽丄傾僲乕僪夋慺揹嬌偲偟偰梡偄偨ITO偺孅愜棪偼1.9偱偁傞丅偙偺偨傔丄SiO2傪ITO揹嬌偺捈壓偵攝抲偟偨ONO傪慖戰偟偨丅昞4偼僎乕僩愨墢枌偺堘偄偵傛傞摿惈斾妑偱丄掅壏惉枌偟偨ONO僨僶僀僗偼儌價儕僥傿81cm2/Vec丄S僼傽僋僞乕0.32V/dec偲崅偄摿惈偑摼傜傟偨丅 丂幨恀3偼帋嶌僷僱儖偺昞帵椺偱丄怓嵞尰惈偼NTSC斾80亾埲忋丄岠棪偼R偑20.9cd/A丄G偑34.5cd/A丄B偑5.35.3cd/A偩偭偨丅 僫僲僋儕僗僞儖Si傪僟僀儗僋僩惉枌偟桳婡ELD傪僪儔僀僽 丂掅壏Poly-Si TFT偵戙傢傞桳婡ELD梡僶僢僋僾儗乕儞偲偟偰晜忋偟偰偒偨儅僀僋儘僋儕僗僞儖Si仌僫僲僋儕僗僞儖Si(nc-Si) TFT偱偼丄Industrial Technology Research Institute(戜榩)偑僩僢僾僎乕僩峔憿偺nc-Si TFT傪梡偄偰4.1宆僼儖僇儔乕僷僱儖傪帋嶌偟偨偙偲傪曬崘偟偨丅

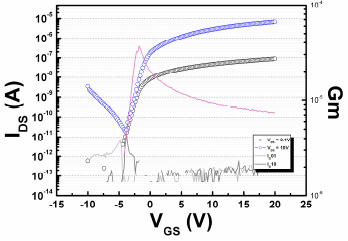

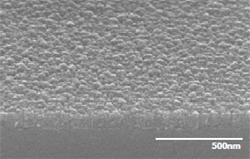

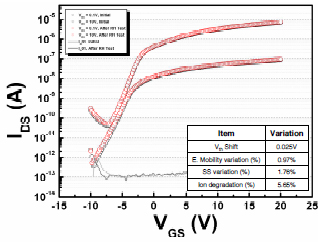

丂僩僢僾僎乕僩峔憿nc-Si TFT偼戞2悽戙儅僓乕僈儔僗傪梡偄偰7枃僼僅僩儅僗僋僾儘僙僗偵傛偭偰嶌惢丅nc-Si枌偼婎斅壏搙200亷丄RF廃攇悢13.56MHz丄RF僷儚乕30mW/cm2埲壓偲偄偭偨忦審偱僐儞儀儞僔儑僫儖側僾儔僘儅CVD朄偵傛偭偰僟僀儗僋僩惉枌偟偨丅僨僶僀僗埨掕惈傪崅傔傞偨傔丄n+ nc-Si枌丄nc-Si枌丄SiNx僎乕僩愨墢枌傪楢懕惉枌偟偨屻丄堦妵偱億僗僩傾僯乕儖偟偨丅幨恀4偼nc-Si枌偺SEM憸偱丄35乣45nm偺僌儗僀儞偑婎斅柺撪偵嬒堦偵惉挿偟偨丅偙偺嵺偺寢徎壔棪偼70亾偱丄攝岦惈偼(111)丄(220)丄(311)偩偭偨丅 丂恾13偼nc-Si TFT(僠儍僱儖挿40兪m丄僠儍僱儖暆160兪m)偺僩儔儞僕僗僞摿惈偱丄Vth偼亅3V丄僉儍儕傾儌價儕僥傿偼0.536cm2/V偩偭偨丅傑偨丄婎斅柺撪偺1噊暆偵偁傞屲偮偺TFT摿惈傪昡壙偟偨偲偙傠丄Vth僶儔偮偒偼1.44亾丄儌價儕僥傿嬒堦惈偼4.37亾偲椙岲側寢壥偑摼傜傟偨丅偙傟偼丄慜婰偺億僗僩傾僯乕儖岠壥偵傛傞偨傔偲峫偊傜傟傞丅恾14偼SiNx枌偱僷僢僔儀乕僔儑儞偟偨nc-Si TFT傪60亷丄90亾RH娐嫬偱嬱摦偝偣偨嵺偺摿惈偱丄250帪娫屻偺Vth僔僼僩偼傢偢偐0.025V丄揹棳掅壓偼5亾埲撪偵夁偓側偐偭偨丅

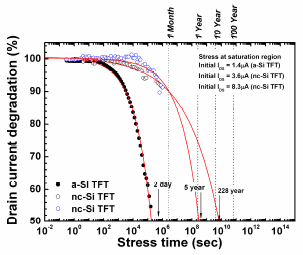

丂廃抦偺傛偆偵丄桳婡ELD傪嬱摦偡傞偵偼1兪A埲忋偺DC僗僩儗僗傪報壛偟偰傕TFT摿惈偑埨掕偱偁傞昁梫偑偁傞丅恾15偵DC僗僩儗僗偵懳偡傞僪儗僀儞揹棳埨掕惈傪帵偡丅DC僗僩儗僗3.6兪A偱偼a-Si TFT偼傢偢偐2擔偱僪儗僀儞揹棳偑敿尭偡傞偺偵懳偟丄nc-Si TFT偼228擭傕傕偮偙偲偑傢偐偭偨丅偝傜偵丄DC僗僩儗僗8.3兪A偱傕nc-Si TFT偺僪儗僀儞揹棳偑敿尭偡傞偺偼5擭偲廫暘側埨掕惈偑偁傞偙偲偑傢偐傞丅偄偆傑偱傕側偔丄偙傟偼桳婡ELD傪僪儔僀僽偡傞偺偵傑偭偨偔栤戣側偄偙偲傪堄枴偡傞丅恾16偼DC僗僩儗僗報壛慜偲報壛屻偺I-V摿惈偱丄DC僗僩儗僗3.6兪A傪106昩報壛偟偨屻偺Vth僔僼僩偼傢偢偐0.16V偩偭偨丅 丂幨恀5偵帋嶌偟偨4.1宆僷僱儖(240亊108夋慺)偺昞帵椺傪帵偡丅2TFT仌1C(僪儔僀價儞僌TFT丄僗僀僢僠儞僌TFT丄僗僩儗乕僕僉儍僷僔僞)峔惉偺儃僩儉僄儈僢僔儑儞峔憿偱丄奐岥棪偼43.2亾丄婸搙偼150cd/m2丄僐儞僩儔僗僩偼10000:1偑摼傜傟偨丅

嶲峫暥專 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| REMARK 1)Stella捠怣偼FPD仌PCB娭楢僯儏乕僗偺柍彏採嫙僐乕僫乕偱偡(僗僥儔丒僐乕億儗乕僔儑儞偑FPD傗PCB偦偺傕偺傪惢昳壔偟偰偄傞傢偗偱偼偁傝傑偣傫)丅 2)偙偺婰帠偼僗僥儔丒僐乕億儗乕僔儑儞 揹巕儊僨傿傾晹偑庢嵽偟偰婰帠壔偟偨傕偺偱偡丅 |